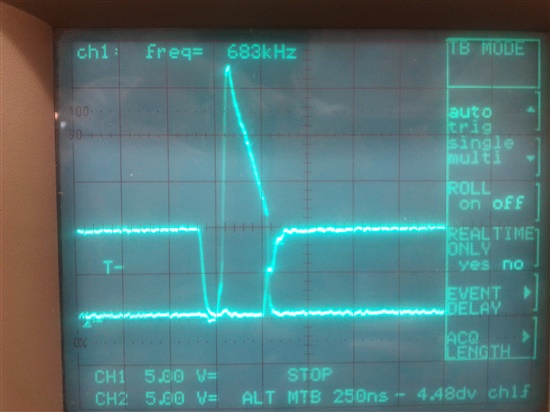

We have couple of DC/DC converters on our board based on TPS40055. 28V to 3.3 (3A)etc... This one has a switching frequency of 683KHz.

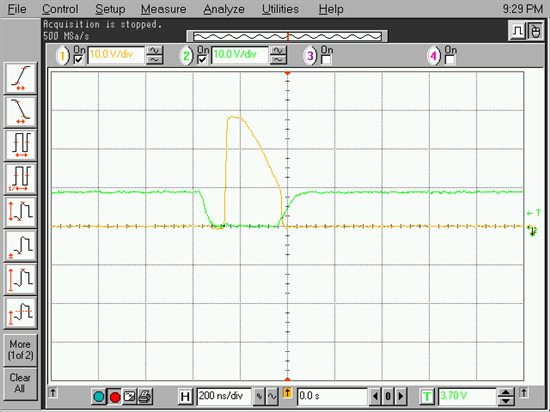

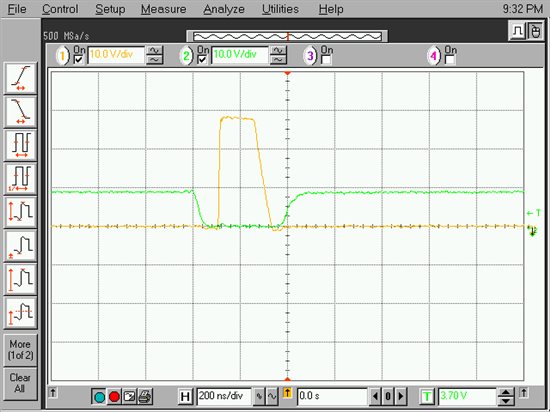

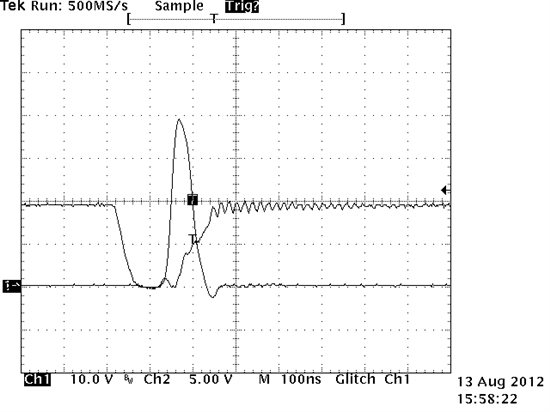

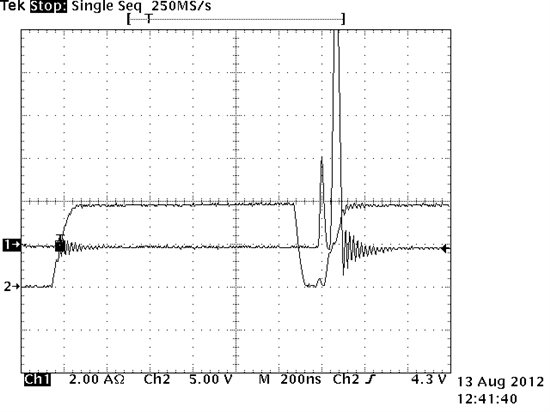

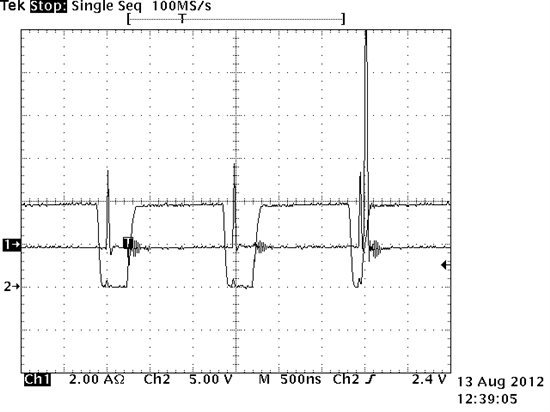

We are seeing that some of the rails are showing a very low (or none) delay between the SR fet turn On and Primary switch turn off. Please see the attached waveforms: (the smaller trace is the Vgs of the SR fet and the other trace is the voltage at the switch node)

The gate voltage of the Primary fet is very similar to the switch node voltage ( 5 to 7 volts higher amplitude)

Most of the time, the waveform looks like the second waveform, but occasionally the shoot through is observed as seen in firstwaveform. Although the circuit seem to work without too much heat dissipation in the current revision of boards, changing the Mosfets (to one with lesser gate charge Qgs ) makes the problem worse.

Currently we use the Vishay part SI4470EY (obsolete now). We tried using the parts si4840bd and si4124dy and the problem gets worse

SI4470EY and si4840bd are listed in the switcher pro database for this design. 1.Is it possible to adjust the turn on times of the SR fet in this chip. How? 2.Looks like the turn off the primary switch is very slow compared to turn On , Is this normal?

After going through the support forum , I checked the volatges at all the pins of the controller and they are normal. Please provide suggestions to solve the shoot thoough problem.

Thank you

Ashok