Hi All,

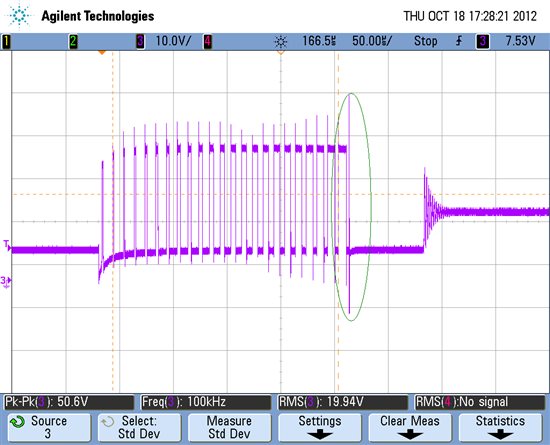

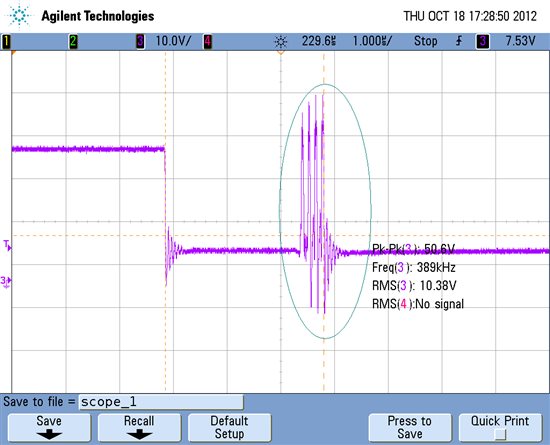

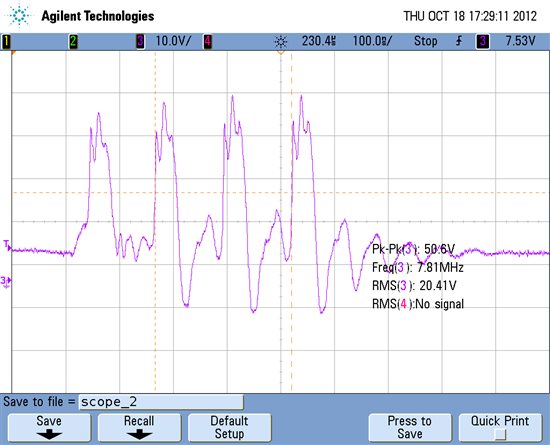

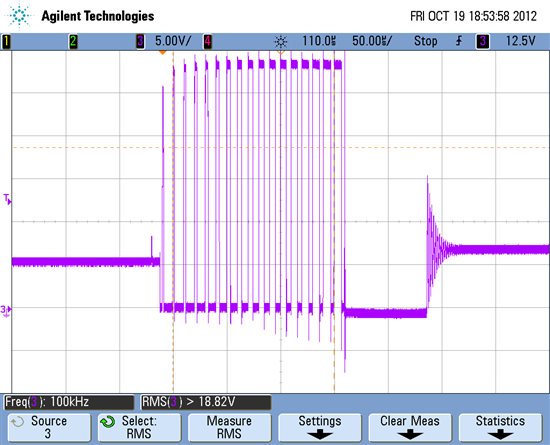

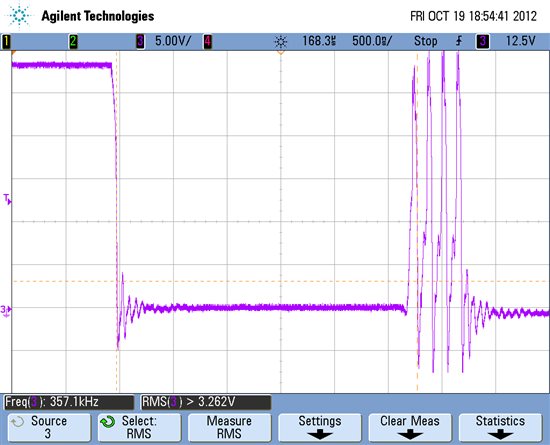

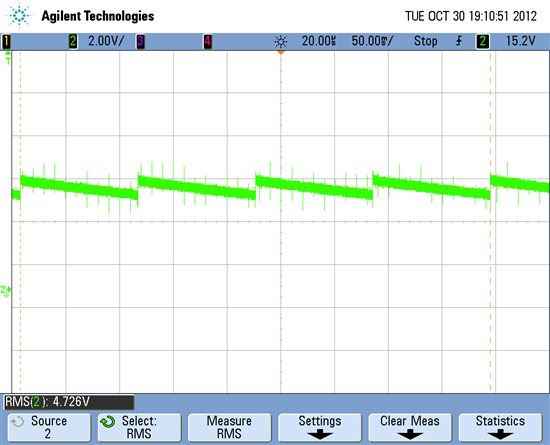

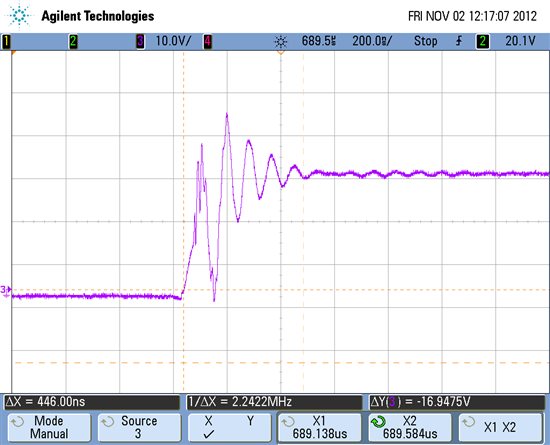

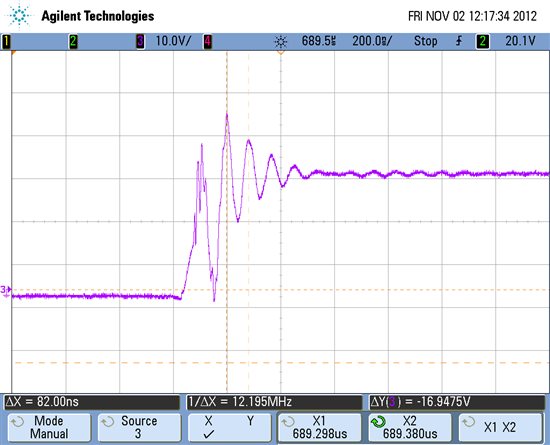

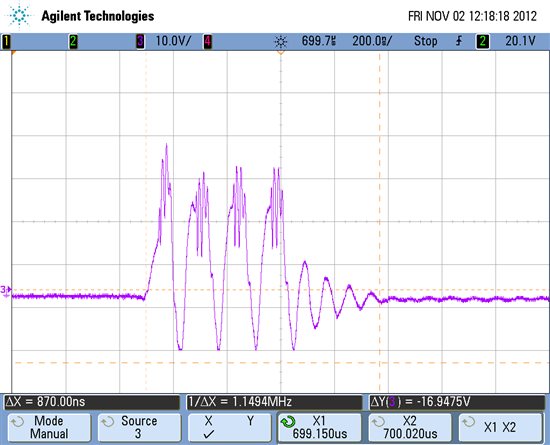

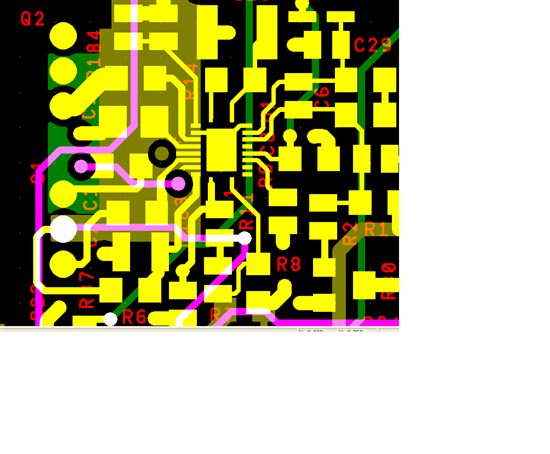

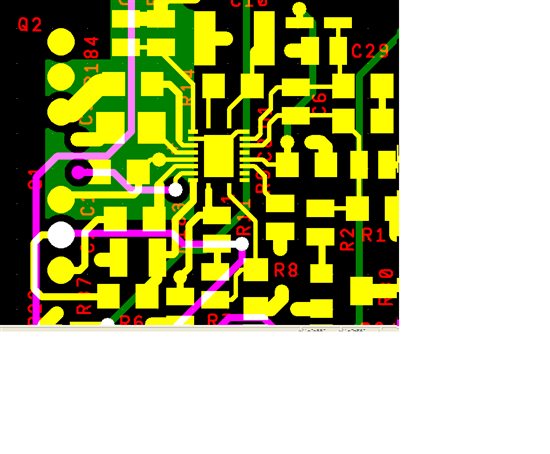

I am using TPS40170 in my buck converter. Input 18-32 V, Output - 15V, Max current - 4A. When I observed the SS capacitor, it is found that the voltage switches between 2.5V and 300mV, indicating that there could be some fault condition(Temperature, OCP and SCP), As I have not connected any load, OCP and SCP cannot happen. Even the device is found to be very cool which concludes that there is no over temperature fault. I have left out with, ringing, which causes the scp or ocp condition. I have noticed ringing on the high side gate pulse with a frequency of 8MHz which causes the device to shut down. The ringing occurs when the HIgh side mosfet, switches on, which in turn trigger SCP (as i believe) The same ringing frequency is seen in boot capacitor also. I am using a boot cap value of 100nF. The MOSFET used was IRF540Z. We have used our own custom board. I have tried all known methods to avoid the condition like adding a series R to boot cap or changing the value of boot cap, addition of snubber circuit at the SW node etc...etc...Kindly anyone help to resolve the issue.