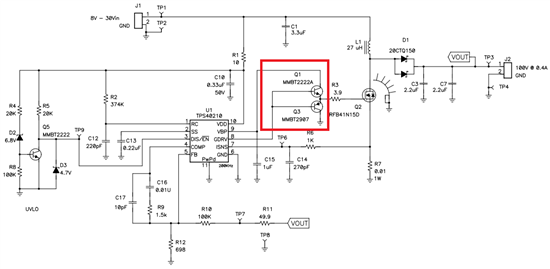

I've built a boost converter, 12V->180V, using TPS40210. I am trying to replace a design based on a MAX1771.

The new design works, and at a first glance behaves great: low ripple, no significant noise anywhere in the circuit, behaves nicely under load. Problem is, the efficiency is only 45% at 13 mA load! I expected to get at least to 75%, which is what the similar circuit using the Maxim part gets.

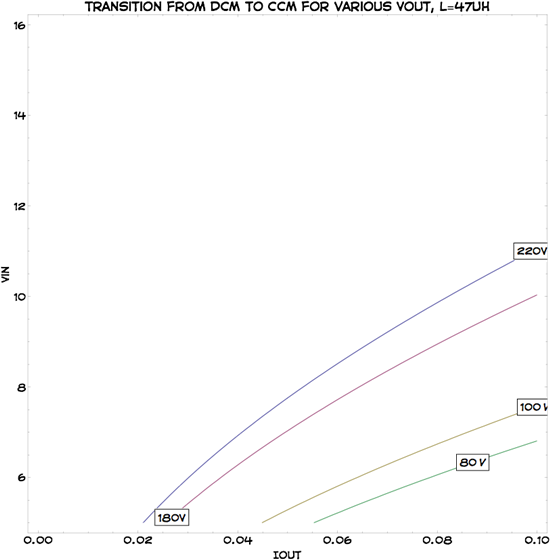

I expected to be able to get up to 85mA @ 180V from this circuit. The (shielded) 100uH inductor has a peak current of 2.4A (the inductor is MCSDRH125B series from Multicomp). The MOSFET is an IRFH5025, with RdsON=84mOhm, Qg=37nC, Qgs=8.3nC.

The losses seem to be incurred in the inductor, as this is the part that gets hot after a short time. Now, I'm puzzled, because I'm comparing this board to one just next to it: the other one is based on MAX1771, uses the same inductor and an IRF644, which has much worse parameters (RdsON=280mOhm, Qg=68nC, Qgs=11nC). And in spite of many problems (noise in the feedback circuit, ringing, etc) has no problems reaching 75% efficiency with the exact same load. The inductor doesn't even get warm. So why does it get hot on the TPS40210 board?

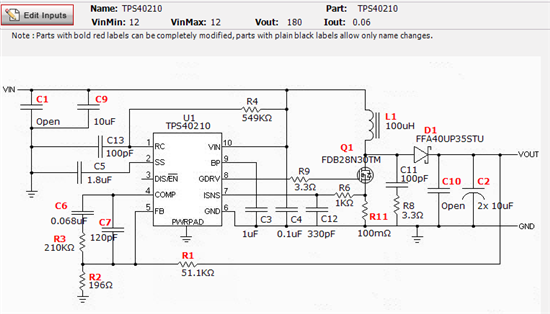

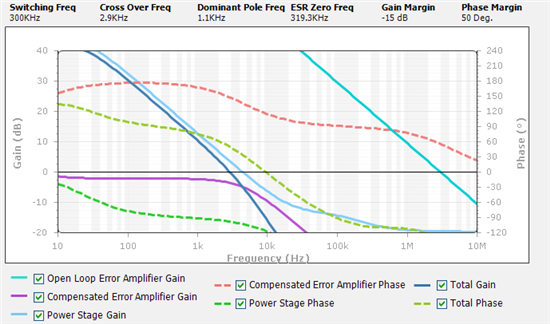

I am posting the relevant part of the schematic and the switcherpro output, which this design is based on (please ignore the double inductor, it is there only to provide pads/vias for both SMD and THT inductors). I can also post pictures of the PCB design and the assembled circuit itself.

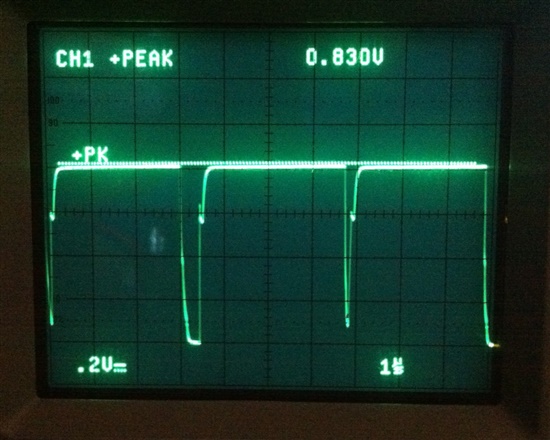

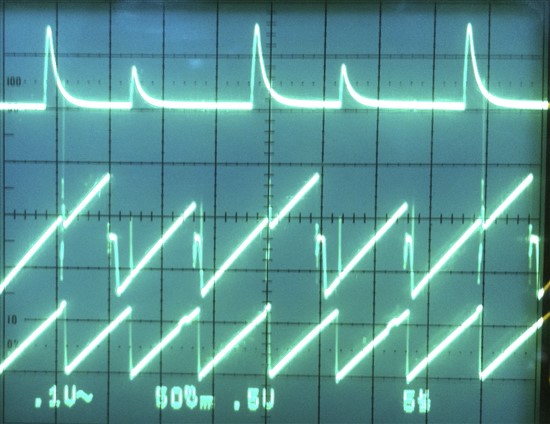

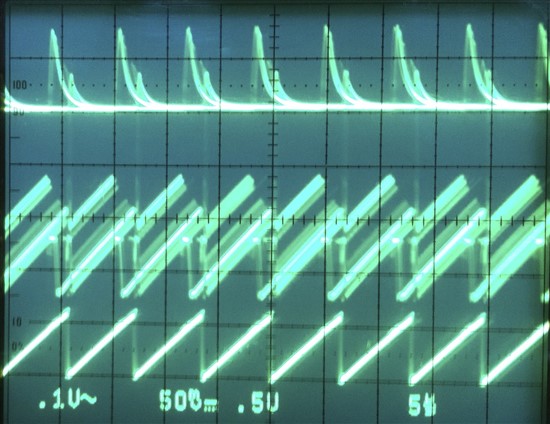

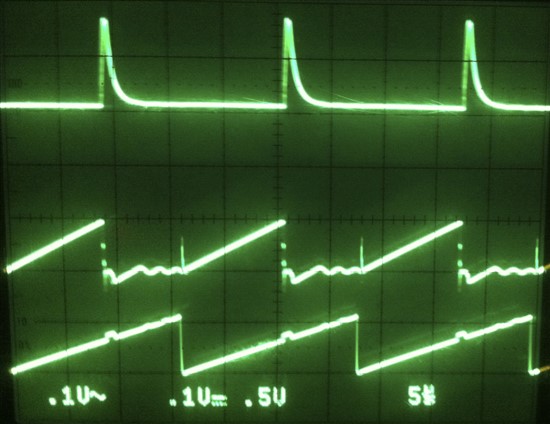

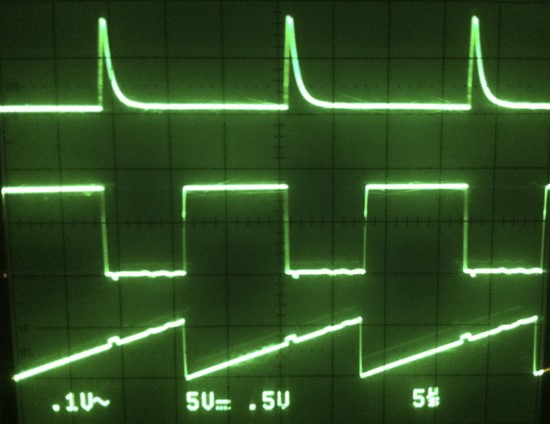

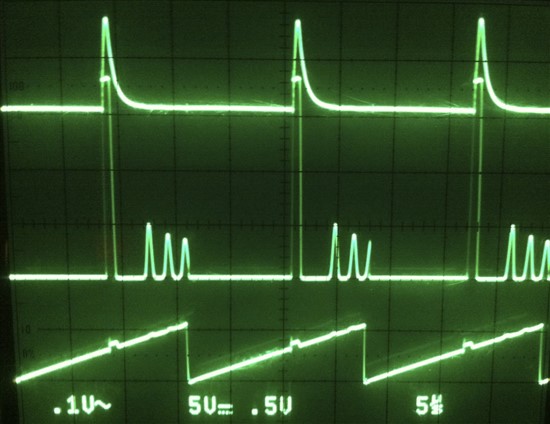

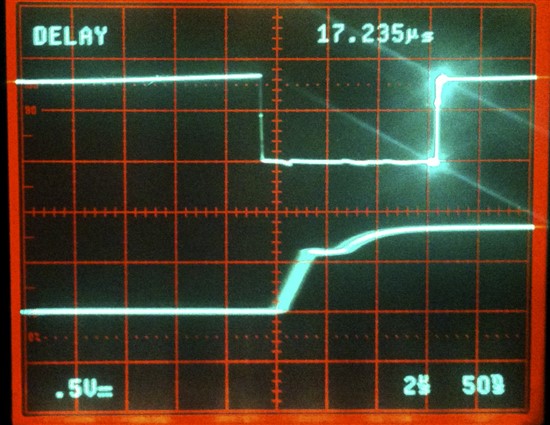

Also, I'm attaching a picture of the gate signal of the MOSFET, taken with a 10x probe. I find the duty cycle highly suspicious.

I've searched the forum for past replies to similar problems -- and in many cases it is suggested that Qgs of the MOSFET might be the problem. But if so, how does the MAX1771 manage to perform much better even with a much worse MOSFET?

Looking for help and advice from more experienced colleagues. Any hints appreciated!