HI,

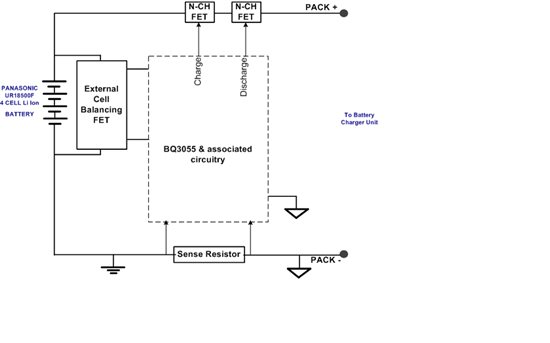

For the BQ3055 battery management design, we have connected the electrical gnd of the battery negative terminal to the battery management chip and its associated circuitry and a separate analog gnd for the point of contact to the charger kit.

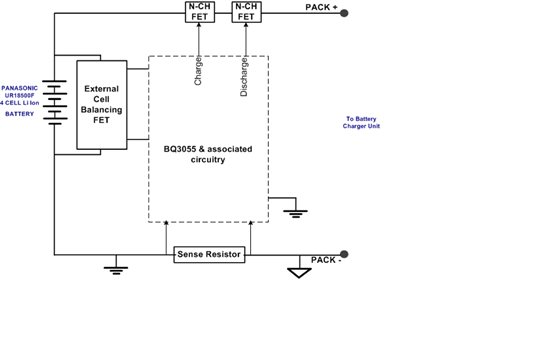

Should the analog gnd for the point of contact to the charger kit be same as the gnd  of battery management chip and its associated circuitry and a seperate gnd for the battery negative terminal or should it be the like the one i have stated in my previous comment

of battery management chip and its associated circuitry and a seperate gnd for the battery negative terminal or should it be the like the one i have stated in my previous comment

i have attached block diagram of both the representations and let me which one is correct

Block Diagram 1