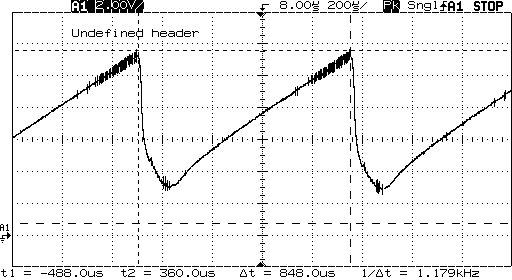

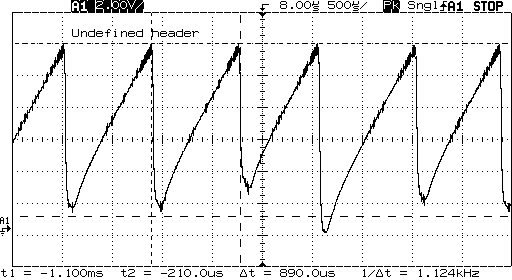

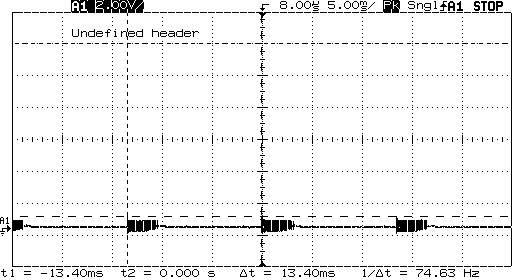

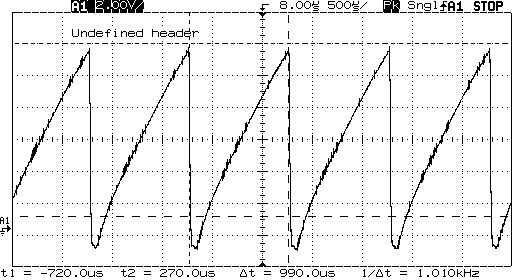

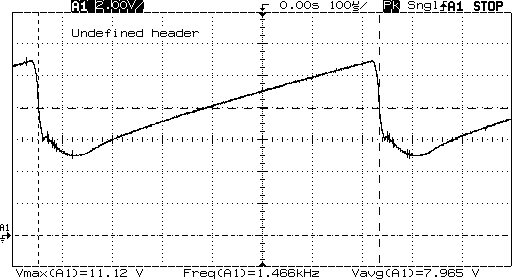

I'm currently trouble shooting a design based around the TPS23756. It is based on a mix of the various flyback reference design for this series of parts, and is to have an output of 5V/3A. The result I'm getting on the output is a sawtooth wave from 2V to 12V at a frequency of 1kHz (screen shot attached). I've double checked the math for all components and made some other tweaks, however I'm having no luck. If anyone has any suggestions as to where to begin looking it would be appreciated.

Are schematic and layout files available for the boards used in SLVA475 and SLUA469? I realize these are very different designs, but if I can't resolve the issues with my board quickly I'm considering just rehashing my design mimicking SLVA475 as close as possible, while also introducing elements of SLUA469 to make sure the EMC is clean.