Hi everyone,

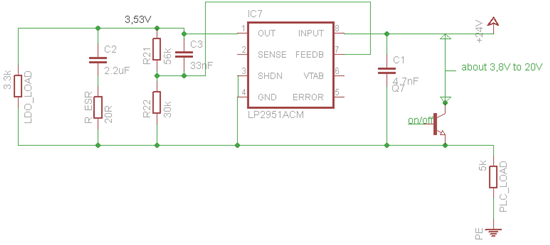

I use the LP2951 in a special configuration. A schematically picture is added below.

The problem is, that the ground of the LDO lies not on the power-supply-ground. Between power-supply-gnd and LDO-gnd is a resistor that is variable.

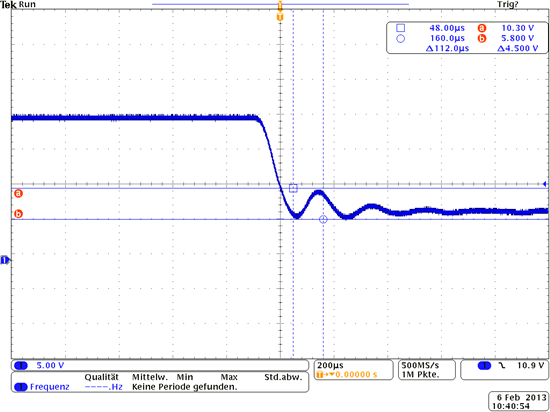

Because of this the LDO runs NOT stable. It comes along, that the input-capacitace of the LDO must be small for my application.

If I raise the ESR, the LDO runs stable. Why is this so? How can I simulate bode plots or something like this to visualize and explain the problems?

Are there formulas for this configuration, that gives the poles and zeros?

Regards