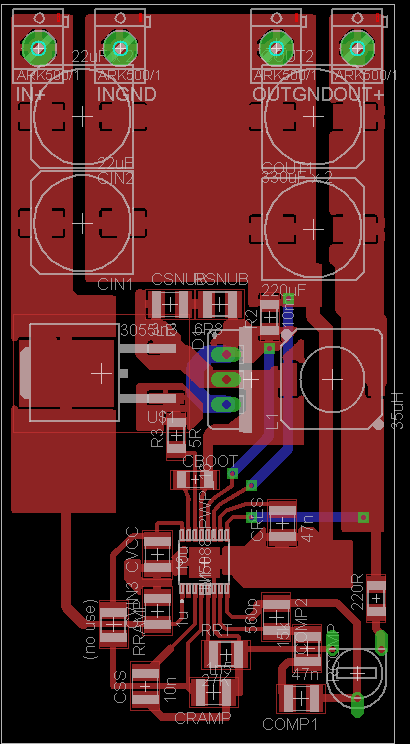

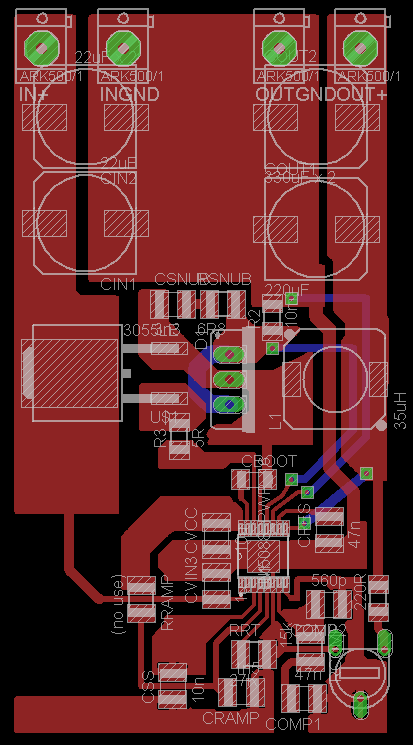

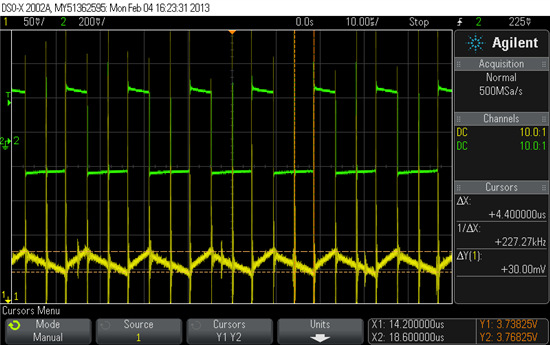

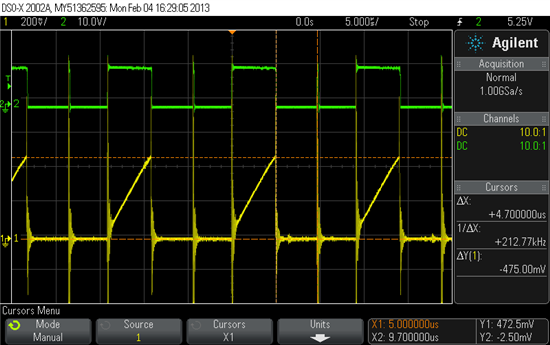

Hello,

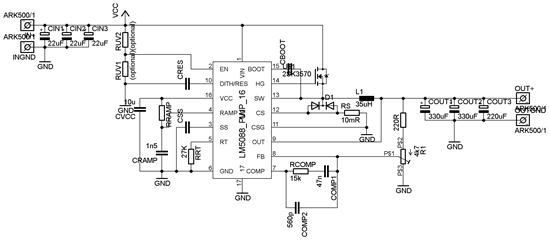

i am learning using buck regulators. I've designed LM5088-2 for input 12V and output 4V (frequency chosen 220kHz). I have problem with finding correct loop compensation. I've chosen 35uH inductor (for low ripple current), 880uF electrolytic output capacitor, measured voltages at SW, FB and RAMP. Is this "pulse skipping" problem of compensation ? (Compensation with Rcomp=15k, Ccomp=47n, Chf=560p) In my case output ripple voltage and transient response isn't much important. How musch is ESR of output capacitor important for correct compensation ?

Many thanks.

Michal

SW and Vout

SW and RAMP

SW and FB

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.