I designed a switching regulator circut using the TPS5450 regulator with a 24V nominal input and a 3.3V output. I needed to support 5A for short term start-up (less tha 500ms) with an average current around 3A. Initially, I designed the circuit using the classic energy balance equations with some inductor and output volatge ripple targets. Later, I used the SWIFT software and found that the 10uH inductor I initially chose was increased to 22uH. I selected a 22uH inductor with an Isat of 6.8A at a 10% drop in L. I also used two 330uF, 25 mohm ESR capacitors even though the design only required one capacitor. My hope was that since output ripple is the product of the inductor ripple current and the ESR I could reduce ripple and mainatin loop stability with the reduced ESR.

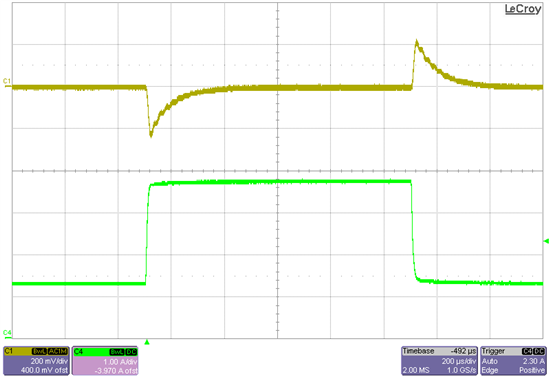

The problem is that when I subjected the regulator to a pulsed (10% DC at 1KHz) 3A load, I saw more than 160mV of load volatge deviation. I measured using an SMA connector directly across the output capacitor and a direct coaxial cable connection to my scope so I believe I saw minimal B-field effects. This much more deviation that I expected and I had hoped to have good load transient response up to 5A not just 3A.

I have a couple of concerns about my design but lack the experinece to know if these issues are the casue of my problem. One concenr is that my layout loop that includes the TPS5450 PH pin to clamp diode and back to ground may not be small enough and could have some additional series inductance. I modeled my design from the data sheet but later realized the reccomended layout in the SWIFT software was different. Although I tried to use wide top copper areas for this node and loop, could too much series inductance in the diode path cause the poor load response?

Secondly, this regulator circuit is fed via an input filter network located on another assembly. The filter includes a 10uH series inductor. Of cource, I have low ESR ceramic input capaqcitors at the TPS5450 input but I see some ringing synchronous wit the load switching. I used a scope probe with a low-L ground clip but my probing could be suspect. At the switching regulator input pin, I have two 4.7uF, 50V, 0805 X5R capacitors. I relaize that the effectve capacitance at the 24VDC bias is much lower than 10uF. Could either my input capacitor selection, whih uses small package capacitors that exhibit degraded capacitance wit yh DC bias or my use of tghe remote input filter be the cause or a contributing factor to the observed poor load transient response?

Thank you in advance for any help or guidance.

Craig