Hi,

I am facing an issue with a Watchdog/supervisor TPS3813K33.

The TPS is resetting the ECU by itself before the first trigger of the WDT pin.

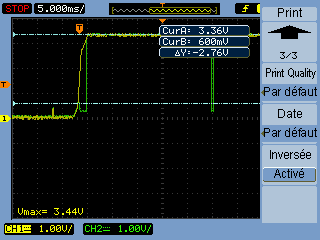

In fact the RESETN pin is not held low for Td timing (25ms low state of RESETN at startup) like in the description, when the VCC is 3.3V, the RESETN is high, and after 25ms, the is a low state of the RESETN pin that make the CPU reset.

Normally, after power on, the refresh frame is inactivated until the first trigger of the WDT pin, so the CPU should not be reset.

Is there someone who have already faced such an issue?

Why the Td time is not respected by the TSP3813K33, is it programmable?

Thanks for you support.

Damien