Hello,

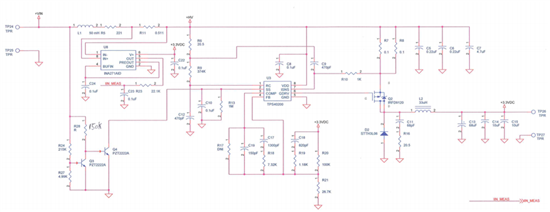

We are using the TPS40200 Voltage Mode Controller in a 50 VDC input voltage application.

We must ensure that the output does not start switching (SS must be held low) until the input reaches 30 VDC. If SS is not driven low the output starts switching at an input of ~5.5VDC.

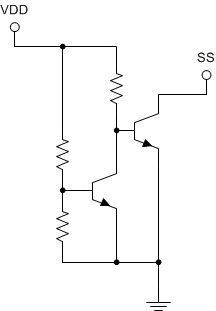

The voltages available for this hold down circuit are the 0-50 VDC. One idea was a comparator with one input fed by the input voltage through a resistor and held at a level using a zener diode and one input on a voltage divider fed by the input voltage. The VCC for the comparator would also be held through a resistor with the otther end tied to the input voltage using a zener. The initial problem with this is the VCC must reach at least 3 VDC before the the input reaches ~5.5 VDC so the resistor must be a fairly low value. The application is very low current and consumes too much current through the resistor and the zener.

David Robinson