Dear Sir/Madam,

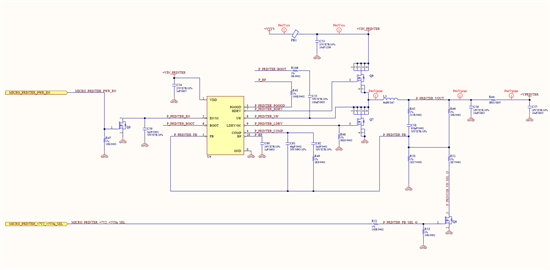

The circuit description that follows can be referenced to Figure 14 in "SLUS964A –NOVEMBER 2009–REVISED AUGUST 2012".

It is intended to dynamically change the feedback resistance (R5) to alter the output voltage. This is accomplished using an NMOS FET and resistor in parallel with R5.

The NMOS gate is tied to GND using a 10K resistor to ensure +5V0 output is default unless driven high by micro.

It has been observed that if EN/SS pin is tri-stated (TPS40305 enabled) and the feedback resistance is changed the TPS40305 is damaged.

Appears that the parts does not start and the LDR/OC drive is damaged. You can see a periodic saw tooth waveform on C1 of less than 1V and the

FB voltage is less than 0.6.

Interestingly if you do the following the TPS40305 is not damaged and works perfectly.

(1) Pull EN/SS to GND (TPS40305 disabled)

(2) Make the feedback resistance change.

(3) tri-state EN/SS pin (TPS40305 enabled)

It will be difficult to ensure that software does violate this procedure.

My question is, how do i protect the TPS40305 to be able to dynamically adjust the feedback resistance without damage.

Regards Grant