I found a discrepancy between the bq77910a part data sheet and the bq77910AEVM evaluation module schematic for the CPCKN and CCAP pins.

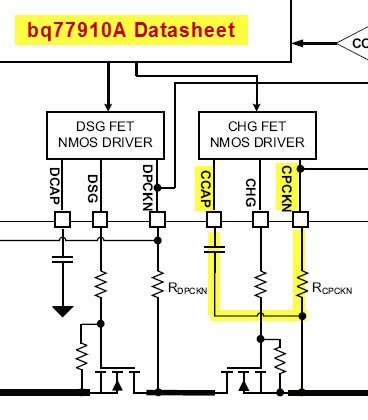

The bq77910A data sheet (SLUSAV6-FEBRUARY 2012) on page 33 shows a series connection of a capacitor and a resistor between the CPCKN and CCAP pins.

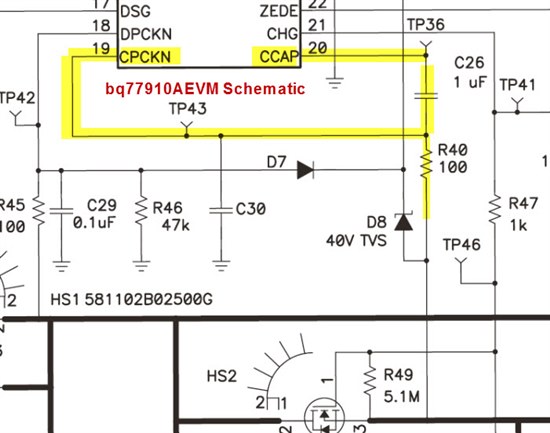

The bq77910AEVM User's Guide (SLUU855-February 2012) on page 30 shows a capacitor connected between CPCKN and CCAP with no series resistor.

Which connection is correct and why?

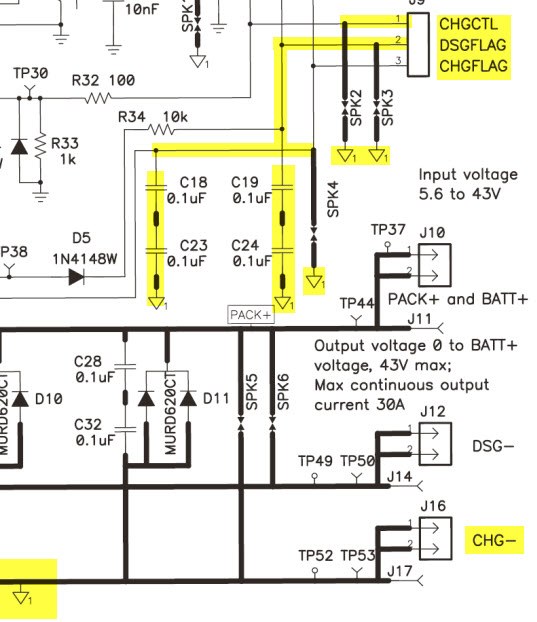

Also, referring to the bq77910AEVM schematic on page 30, what is the purpose to C18, C19, C23 and C24. Why are they both tied to CHG- return. Would it be better to connect the DSGFLAG bypass capacitors to DSG- instead of to CHG-? The spark gaps are also all connected to CHG- ground. What is the the reason for the ground selection.