Hi,

I am using TPS7A4501 LDO in my design.I want to control the LDO output using Shutdown pin from FPGA.

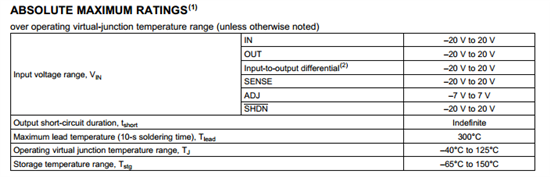

In datasheet no where it is not mentioned supported shutdown pin IO logic.

What is mean by shutdown threshold voltage.Is this any correlate with shutdown pin IO logic.

Can somebody explain this.

Thank you,

Regards

Swapna.B