Hello

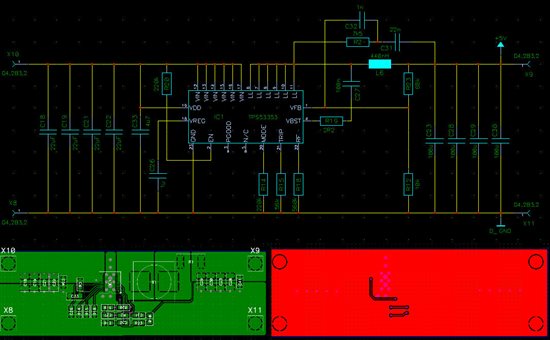

how sensitive the TPS53353 responded to a 2-layer layout?

I make no attempt to run my board.

If I burden the output, the output breaks together

Is a multilayer mandatory?

I think the high MOSFET did not controlled properly.

The Regulated 5V is OK but the PowerGood Pin is low ( with a Pullup Resistor )

Could it be an internal reset that responds to glitches?