Hi,

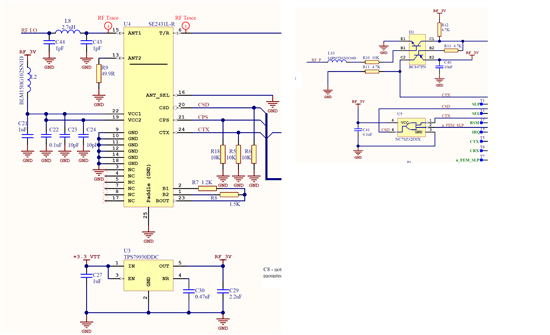

We have used TPS79930DDC LDO to drive a RF Circuitry which consists BC847 BJT, NC7SZ32 OR gate, Front End module(FEM).

I am just elaborating my scenario.... I will my question at last. please bare with me.

It is EN is connected to input itself. NR has 0.47uF Cap to GND.

input voltage 3.3-3.6

Output Voltage : 3.0V

Output Current max going upto 280mA . without exceeding the maximum power dissipation.

we have an Issue, When we driven the FEM sleep mode , the whole circuitry is taking around 157uA of Current.

The variables i can see.

Input leakage Current of OR gate = +/- 10uA

Quiscent Current of OR gate = 20uA

Quiscent Current(Ignd) of LDo - 40uA

Icbo of BJT - 10nA(approx)

there is 1 pull up of 4.7K on Collector to 3V.

Is there any minimum current requirement for LDO, becasue whole current added is <100uA