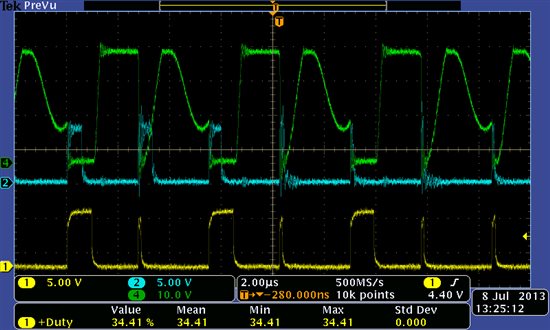

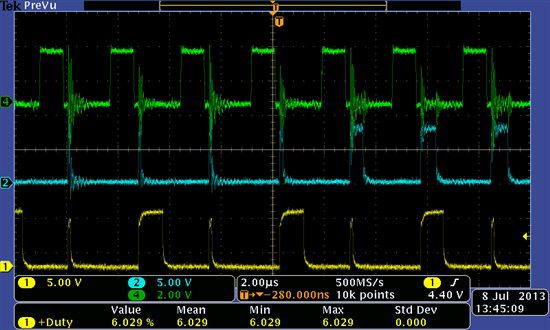

I set the RC to 500K and 470pF which has the Controller running at ~ 100KHz, then using a 1N4148 Diode with the anode connected to the RC junction per the Data Sheet

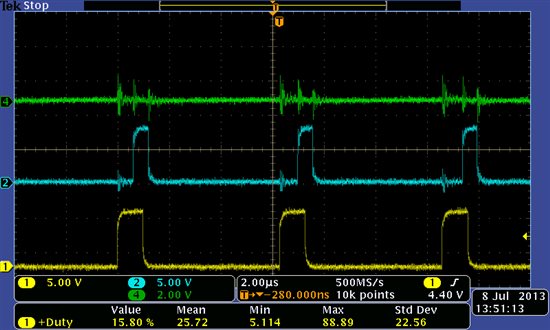

I applied a 5V, 250KHz clock with a 30% Duty Cycle (positive) through a 5.1K resistor. The controller does not seem to like this as I get occasional double pulses and the controller restarts every 100 ms or so. The controller works fine when I disconnect the external clock and set the RC time constant for 250KHz and the Duty Cycle at full load and minimum Vin is ~ 43%............the Data Sheet offers little info on synchronizing the TPS40210 so am I missing something here?