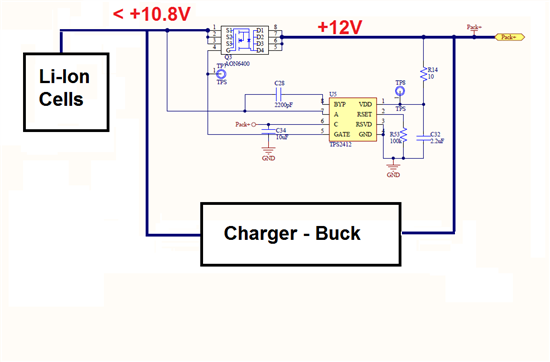

My customer is having a problem with the TPS2410 (see attached schematic).

The ideal diode functions as expected and is used as a bidirectional current control.

The 12V bus is connected to the C pin as per page 22 of the spec sheet (Bidirectional control and blocking).

The issue with the device is when the ideal diode is disabled.

Signal BBU_ENABLE_L is active low, 12V bus goes low and VBAT1 (battery voltage) is 15-20V.

No power can be pulled from the battery but a voltage is measured on the 12V bus in the order of 3V.

The customer is monitoring the 12V bus. If there is a voltage, the host assumes the 12V bus is ok.

What can be accomplished to remove this voltage on the 12V bus?

The voltage is leaking from the resistance between the a and C pins on the controller.

Here are testing results. The C-pin current is way outside of specification. The total current is not accounted for (IN = OUT). It appears that Vac ~= -1.8V is a threshold for sourcing/draining current from the A-pin.

|

Test Name |

C-Voltage (V) |

A-Voltage (V) |

A-Pin current (uA) |

C-Pin Current (uA) |

GND-Pin Current (uA) |

Comment |

Voltage Delta (External - Cell) (V) |

|

Minimum PS-V #1 |

11.64 |

7.2 |

-530 |

|

|

A pin charges the cell stack |

4.44 |

|

Minimum PS-V #2 |

10.11 |

77 |

|

|

A pin discharges the cell stack |

1.53 |

|

|

Minimum PS-V #3 |

10.44 |

176 |

|

|

A pin discharges the cell stack |

1.20 |

|

|

Minimum PS-V #4 |

10.65 |

245 |

|

|

A pin discharges the cell stack |

0.99 |

|

|

Nominal PS-V #1 |

12.20 |

7.2 |

-566 |

1225 |

3074 |

A pin charges the cell stack |

5.00 |

|

Nominal PS-V #2 |

10.11 |

-88 |

1225 |

2999 |

A pin charges the cell stack |

2.09 |

|

|

Nominal PS-V #3 |

10.44 |

12 |

1225 |

2985 |

A pin discharges the cell stack |

1.76 |

|

|

Nominal PS-V #4 |

10.65 |

88 |

1225 |

2977 |

A pin discharges the cell stack |

1.55 |

|

|

Maximum PS-V #1 |

12.36 |

7.2 |

-570 |

|

|

A pin charges the cell stack |

5.16 |

|

Maximum PS-V #2 |

10.11 |

-135 |

|

|

A pin charges the cell stack |

2.25 |

|

|

Maximum PS-V #3 |

10.44 |

-36 |

|

|

A pin charges the cell stack |

1.92 |

|

|

Maximum PS-V #4 |

10.65 |

28 |

|

|

A pin discharges the cell stack |

1.71 |