Dear All,

We designing big project for some company and we need help with our design.

We have two BQ77910a stacked with series fet configuration. Schematics are based on design note: The Basic Circuits for bq77910A Stack Design - SLUA637

When we try to charge the battery, after about 5 minutes BQ set the Short Circuit Charge flag and shuts off the fets. Disconnecting and again connecting the charger clears the flag and again after 5 minutes situation repeats.

How this could be possible when upper BQ have shorted pins: Sense +, Sense - and VSS2 to cell10 (GND of upper BQ)? Does Cell ballancing function can set this flag when something is wrong?

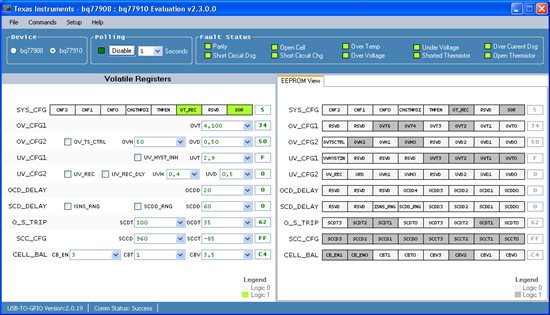

This is the configuration of the upper BQ:

Thanks for any suggestions and help.