Hi

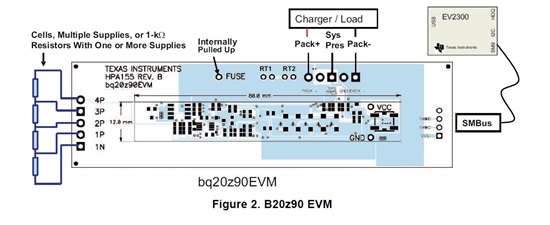

For a new product I'm including the bq20z65R1 to manage 2s LiPo 5300mA batteries.

I made a simplified design, which have been tested on the Eval bord without problem

Now I can charge the battery, with both FET turned ON.

The problem is when I disconnect the charger. The DSC FET is turned OFF, and 2 errors flags are set:

XDSG and XDSGI

To be accurate, with no load, I can read 16V for 1sec, 5.4V for 1 sec, and then 0V. With a load, I read just few mV.

Any idea to help us for this projet ?

Thanks in advance.

Eric