Hi,

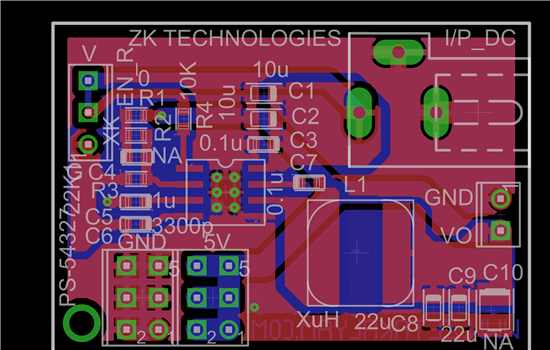

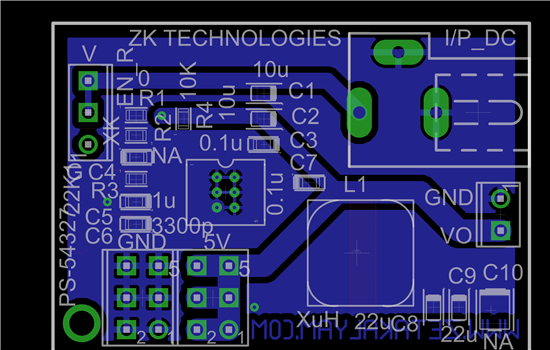

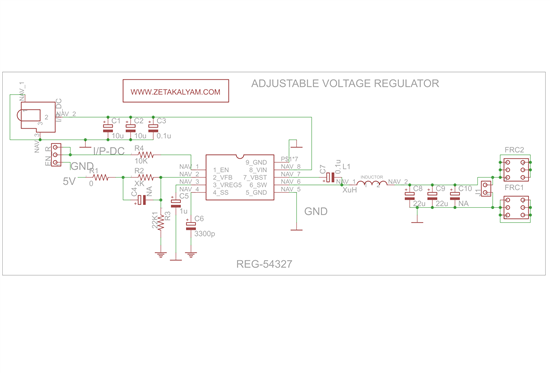

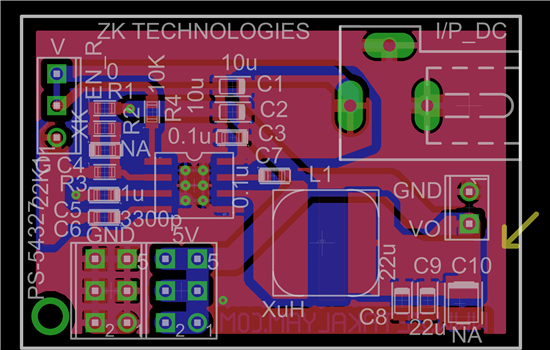

We are using TPS54327 SWITCHING REGULATOR(Adjustable type(i/p=13V and o/p=3.3 to 5V) so some resistors values are mentioned as X and we will choose it from EVM datasheet table) for our device. I have referred TI evaluation layout design for our new design which is shown below. EN pin is shorted to Vin for enable the device. So please check and verify the design and Let me know any changes required for our new design. So that we can give it for PCB manufacturer.

Regards,

Naveen K