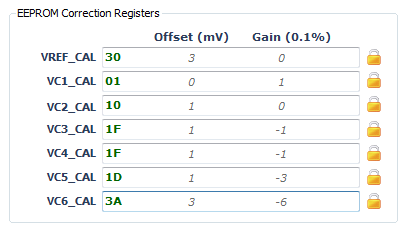

I'm having an issue with figuring out the gain and offset correction of the BQ76925 and how it's being calculated in the Evaluation Softtware.

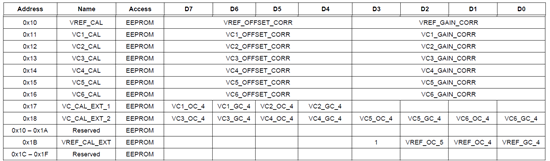

As far as I understand from the data-sheet the values are 5-bit 2's compliment number, except VREF OC which is 6-bit, which we'll ignore. To be negative, the high bit needs to be set just like an 8/16-bit 2's compliment . When looking at the software I see some positive and some negative values.

| Offset(mV) | Gain(0.1%) | |

| VREF_CAL | 3 | 0 |

| VC1_CAL | 0 | 1 |

| VC2_CAL | 1 | 0 |

| VC3_CAL | 1 | -1 |

| VC4_CAL | 1 | -1 |

| VC5_CAL | 1 | -3 |

| VC6_CAL | 3 | -6 |

The issue is when I read the EEPROM out the the I2C either myself or looking at the communications I don't every see the high bit being set. Looking at the comms log I see