Hello,

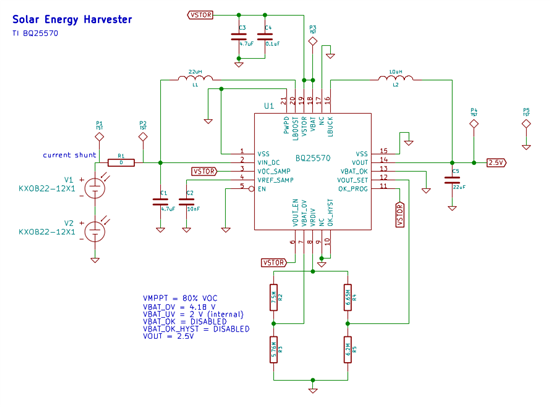

I designed a board using the bq25570. I recently assembled it and am having problems getting it to work properly. I attached a schematic. VSTOR is only charging up to 0.5V. I am not getting anything on VOUT. I am using two solar cells as the power input in a controlled lighting environment which is giving me 1V @ 5mA. I tested this solar input on the BQ25570EVM in the supercapacitor configuration without the supercapacitor attached. I was getting the set voltage of 1.8V on VOUT and a good voltage on VSTOR. So, I verified the solar cells are fine and it seems there must be an issue with the design of my board or an assembly problem. Any idea what could cause VSTOR not to charge up all the way? Please take a look at the schematic and let me know if you see any issues.

Thank you,

-Nick