We are using the 43060 in a 12V to 50V 0.8A boost circuit. Switching frequency is about 300kHz which we are using with Infineon BSC340N8 low gate charge FETs. The chip gets very warm and eventually fails in the corner of the package close to the VCC supply. It seems that the VCC supply is overloaded and doesn't appear to have any form of protection.

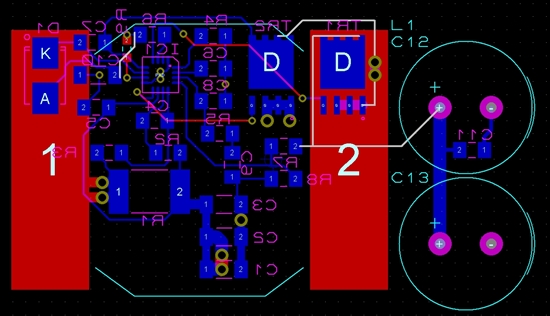

We have added the 2R resistor recommended (on the last line of the data sheet almost as an afterthought) although there's no information about how the value should be selected. The resistor is also shown between the chip and the output cap: is that right?

Should we be increasing the value of the resistor to limit current into the boost diode? If so, by how much?