Hi there,

according to the datasheet of UCC28950, FIG. 7, outF drops after outA. The delay between the two gate signals depends on Tafset (min and max, depending on the voltage at CS pin and adaptive delay settings).

Is it possible that in some configurations outF drops before outA?

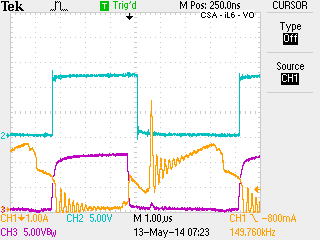

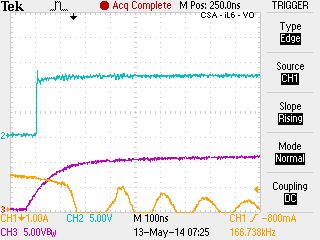

In the attached pictures this is exactly what is happening in my experiments. In yellow is the current of synchronous rectifier E. In blue is the gate signal of Qa and in purple is the gate signal of Qf.

I have Raef(hi)=0 and Raef=70k. Ref is 60k.

Do I have a faulty controller or something is wrong in my design? According to the datasheet this is not the way it should work. As the load current increases, the delay increases and finally outF drops after outA but with a much smaller delay that what I would like.