Hi,

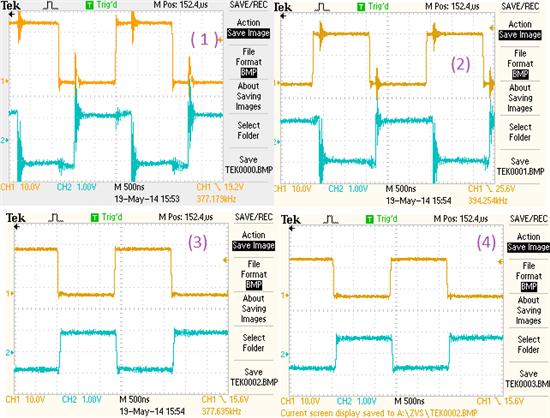

Currently i am using a full bridge phase shifted converter with ZVS topology, i was given a design which had several faults within and have been working through them. Initially there as jittering on the high side MOSFET switching and noise from the magnetics which has been resolved. The design specification is a 24V DC to 350V DC, with a input range of 18V to 30V. Unfortunately when the input voltage drops below 24V the output also decreases. has anyone had similar issues in the past or have any idea what could be the issue, any help is much appreciated.