Hello,

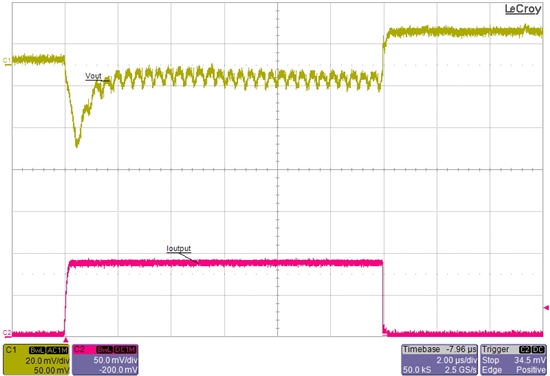

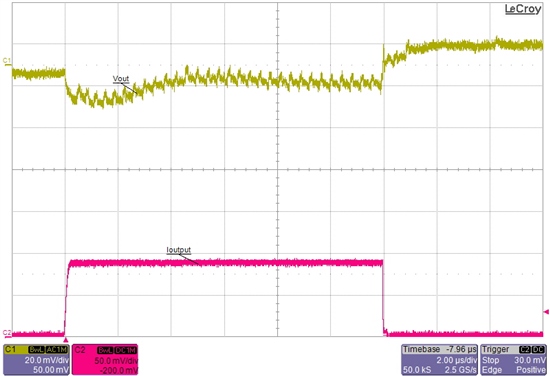

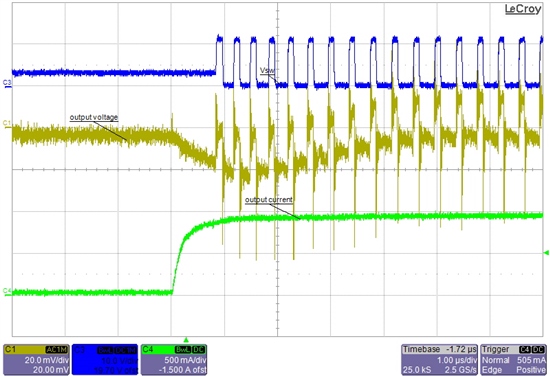

I got similar problem when the load decreases. I used the EVM board:

Load is 0.5A, output voltage is set to 3.3V, Vin is 12V (short wire, 10A power supply).

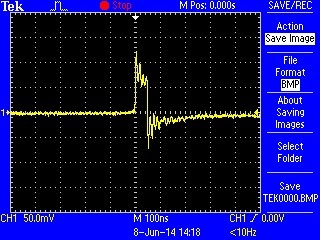

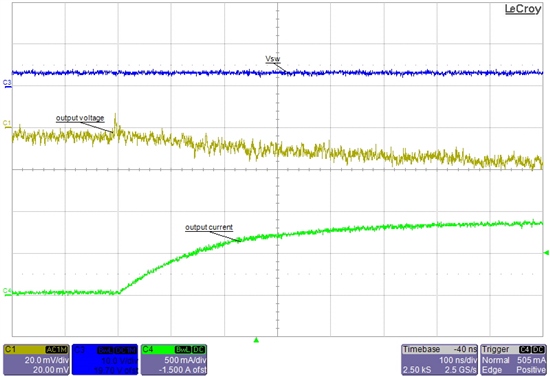

SInce I read this post, I already put a big cap of 100uF on the input and additional 100uF cap soldered on the terminals behind (cannot see in the picture above. Here is what I get: (load is 6.8 Ohms which means about 0.48A)

Please advise how to solve the problem. Increasing Cout does not help so much.