Hi,

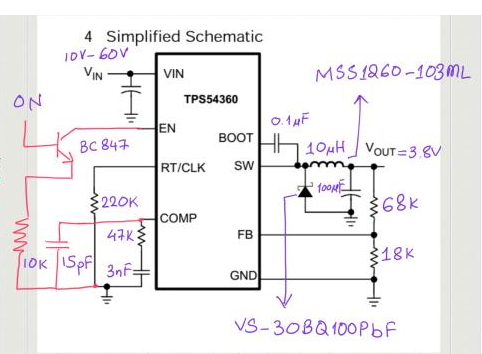

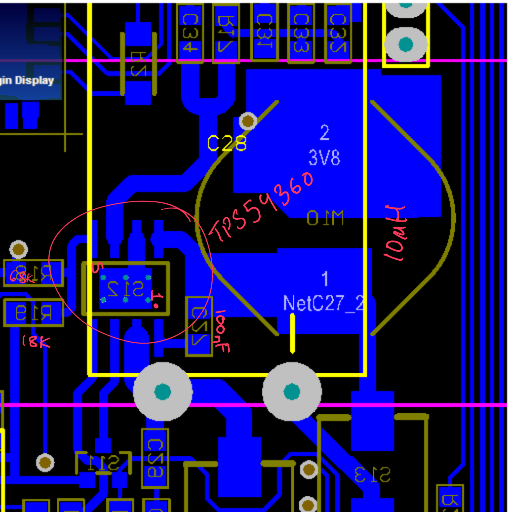

I have designed a power supply for GPRS modem using TPS54360. My Input voltage range is from 8V to 60V and max current is 3A and output voltage is 3.8V

Sorry the values of the RC components with the compensation (COMP) are wrong in the above circuit. I have used R=12k (instead of 47k) and 10nF (in series with this resistor, instead of 3nF) and then 15pF (parallel to the R and C). I have used the formulas in the datasheet to calculate these values. I have gone through the datasheet a couple of times and reconfirmed all the values and everything seems correct.

Everything works fine till 900mA and as soon as I put on some more load the output voltage drops to 1.8 or ~2V (depending on the load) and as a result of voltage drop current also drops.

Can anyone please tell me what am I doing wrong? Thanks in advance.

Regards

Saqib