Other Parts Discussed in Thread: UCC27201

Hello everybody.

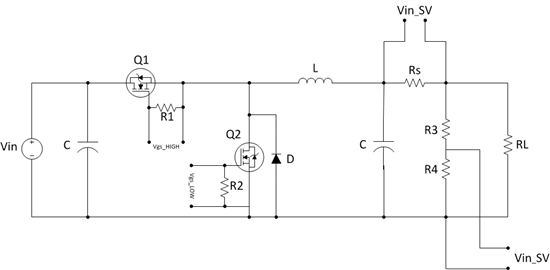

I am making a synchronous buck converter of 200kHz. It’s in open loop right now. A schematic diagram is presented in Fig. 2 and description of circuit elements are detailed on table 1.

Fig. 2. Synchronous buck converter.

Table 1. Elementos del circuito de la figura 2.

|

Elemento |

Referencia |

|

D |

STTH8ST06 |

|

Q1, Q2 |

STFI40N60M2 |

|

Driver |

UCC27201D |

|

Cin |

10uF/50V |

|

R1, R2 |

10KΩ-1/2W |

|

L |

74435584700 WurthElectronics |

|

C |

330uF/100V |

|

Rs |

0,05Ω/5W |

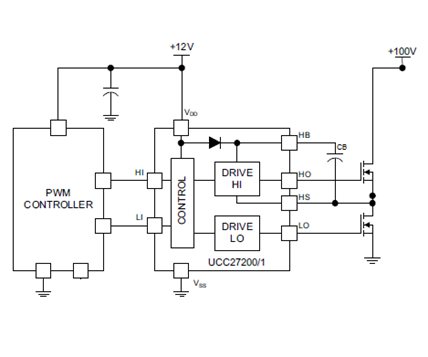

Figure 3 is a half bridge drive to switch Q1 and Q2 MOSFETs. UCC27201 is a 8 pin SOIC package of TI. The implemented circuit has a boostrap capacitor (CB) of 470nF and every MOSFET has a 6.8 Ω resistor in series with gate pins.

Fig. 3. Half bridge driver.

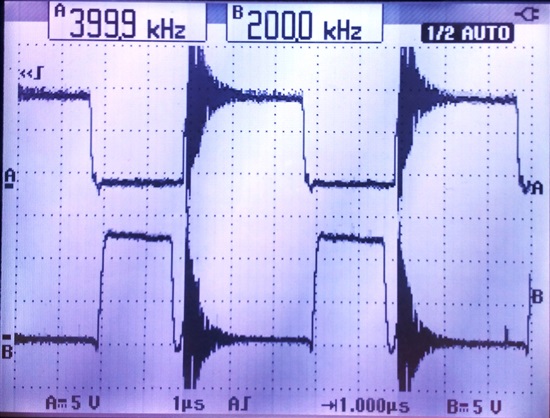

Fig. 4. PWM Q1 signal measured from microcontroller pins.

Fig. 5. PWM Q2 signal measured from microcontroller pins.

Figure 4 and figure 5 are PWM signals for Q1 and Q2 MOFETs, respectively, measured from microcontroller pins without power stage (inductor, capacitor and low). PWM signal has a dead time of 250ns (about 5% of dutycycle).

Fig. 6. Vgs of Q2 measured from MOSFET without power stage.

Fig. 7. Vgs of Q2 measured from MOSFET with power stage.

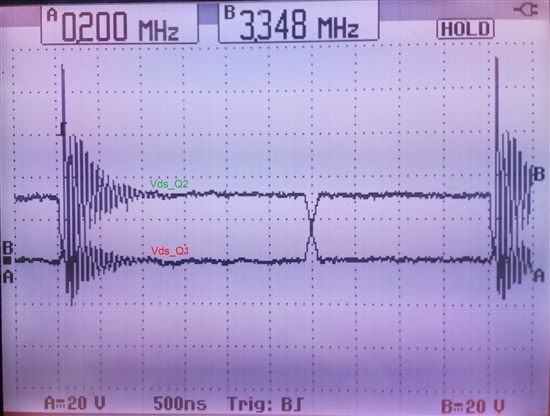

Fig. 8. Top: Vgs Q1, Bottom: Vgs Q2, measured from MOSFETs pins with 30V powered converter and a load of 1.14 A

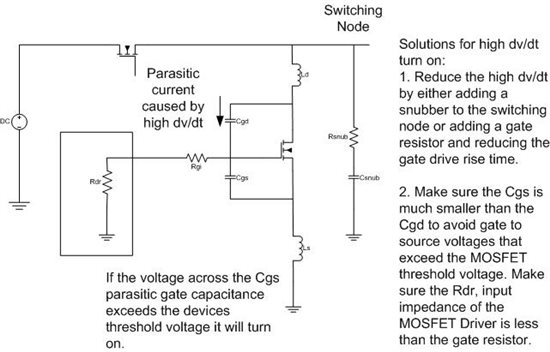

Converter has a 17.2V with a dutycycle of 56% but according to figure 6, PWM signals have high frequency oscillations and when Q1 is turning off and Q2 is turning on, there is a short time when both MOSFETs are ON at the same time (I couldn’t solve this problem even put a dead time of 1us which is about 20% of switching period).

Given that increase the timeout is not enough, How to improve the driving state transition from Q1 to Q2?

Fig. 7. Drain-source voltage.