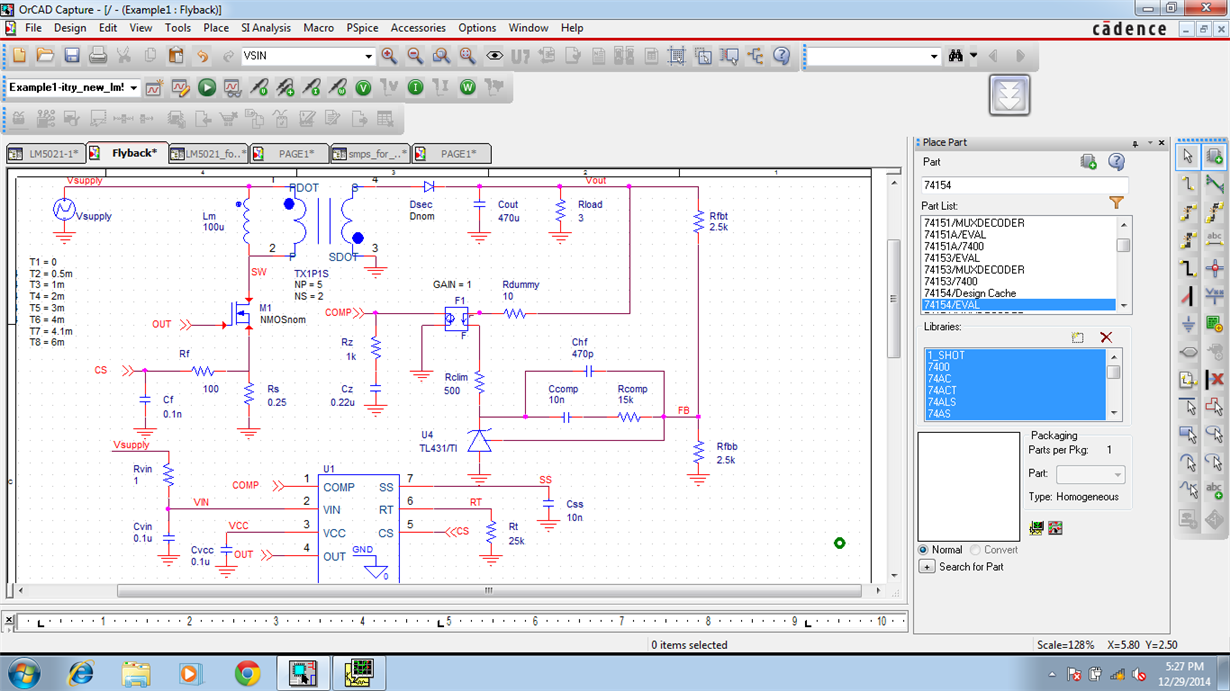

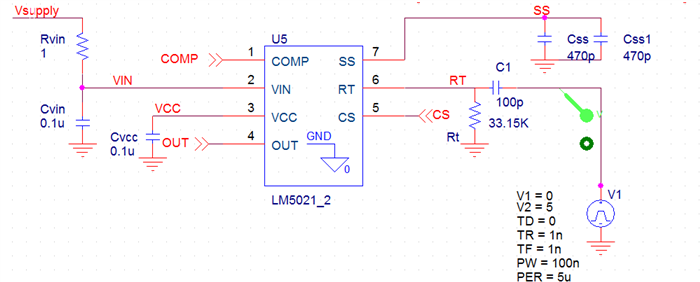

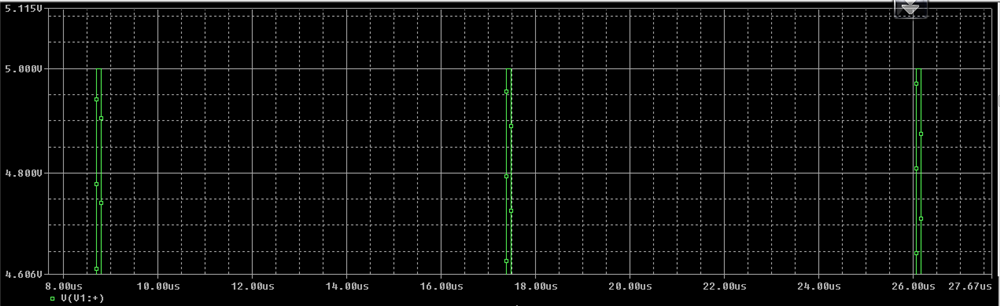

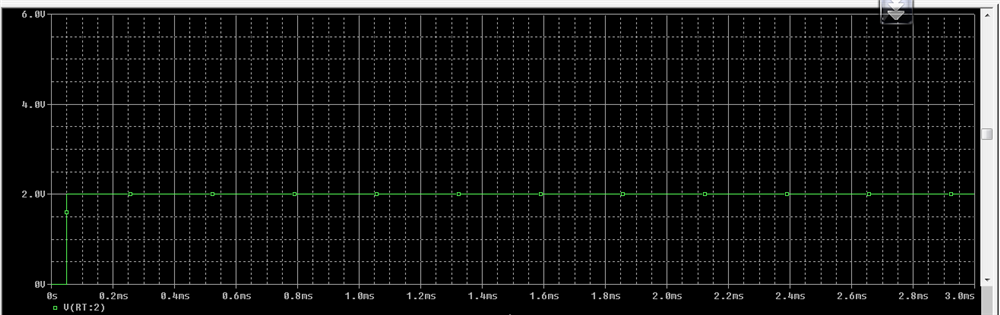

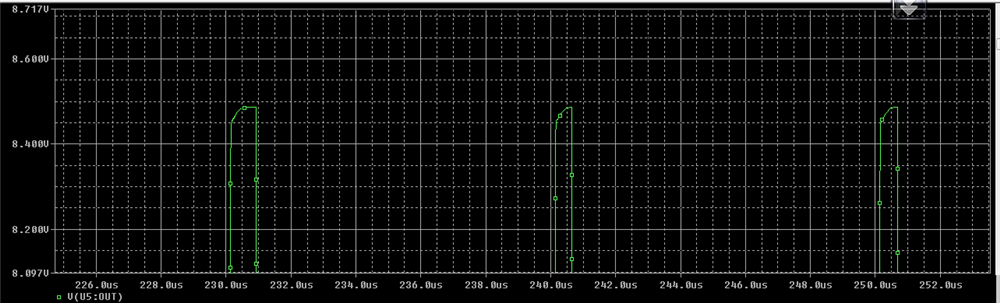

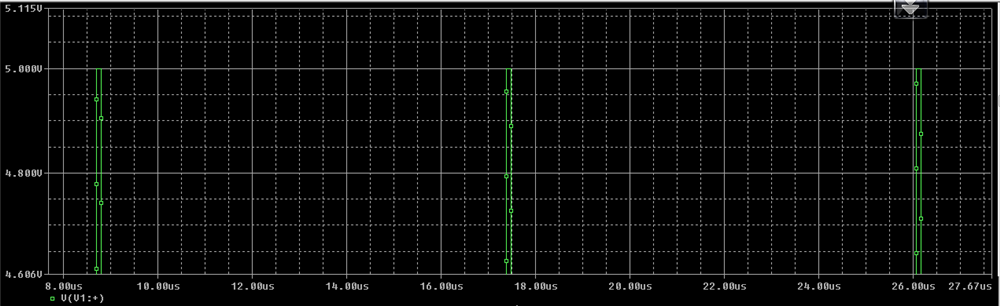

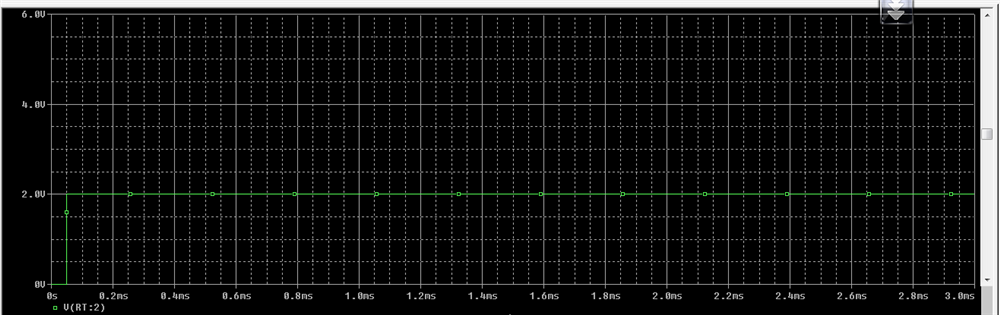

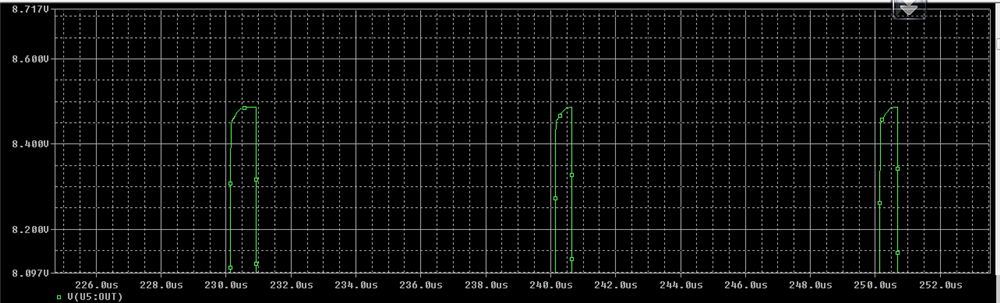

This is an original flyback converter from TI website. If the PWM controller LM5021 is to be driven by an external clock input at pin RT, how would the input circuit at pin RT look like? RT pin is used for external clock synchronization. How should be the external clock signal?? Square wave?? with what duty cycle??

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.