Hi,

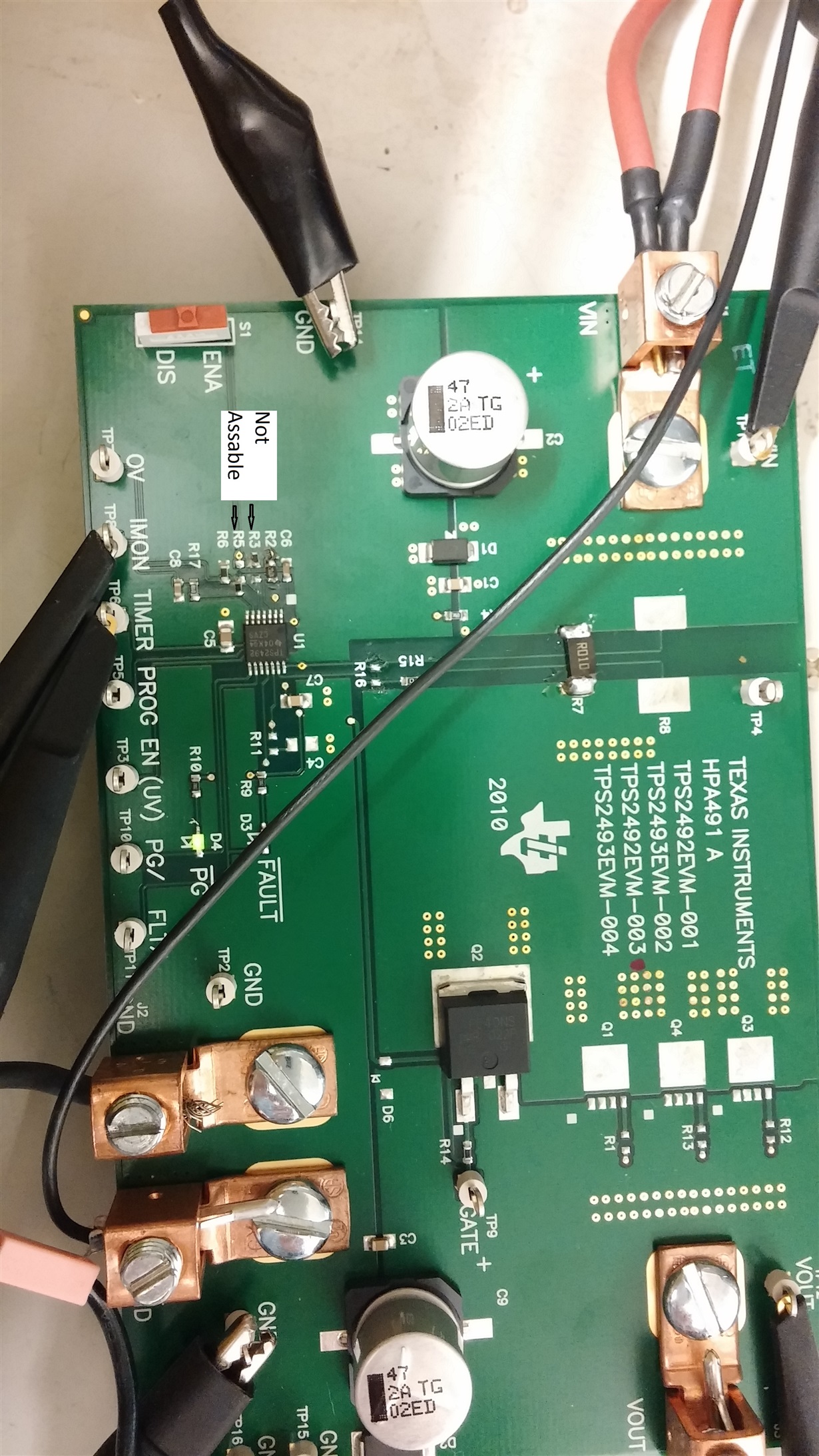

I'm using in my design TPS2492. I'm not intrest in power limit and that's why I put pull-up of 47K between VREF and PROG.

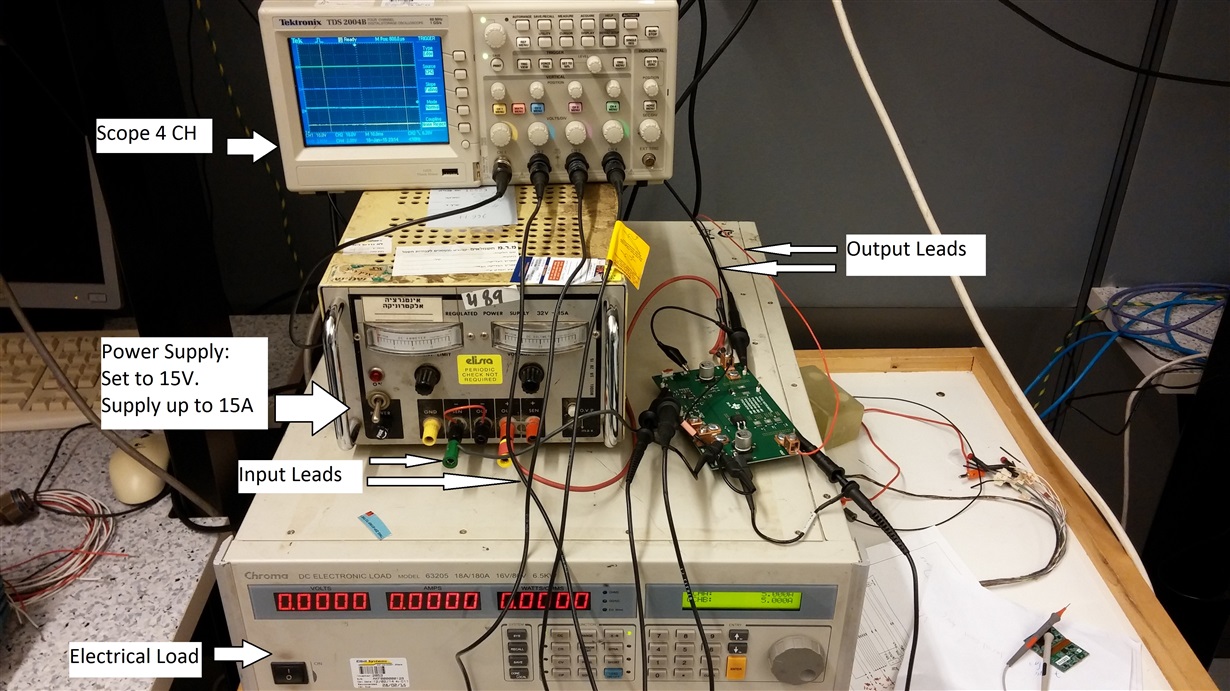

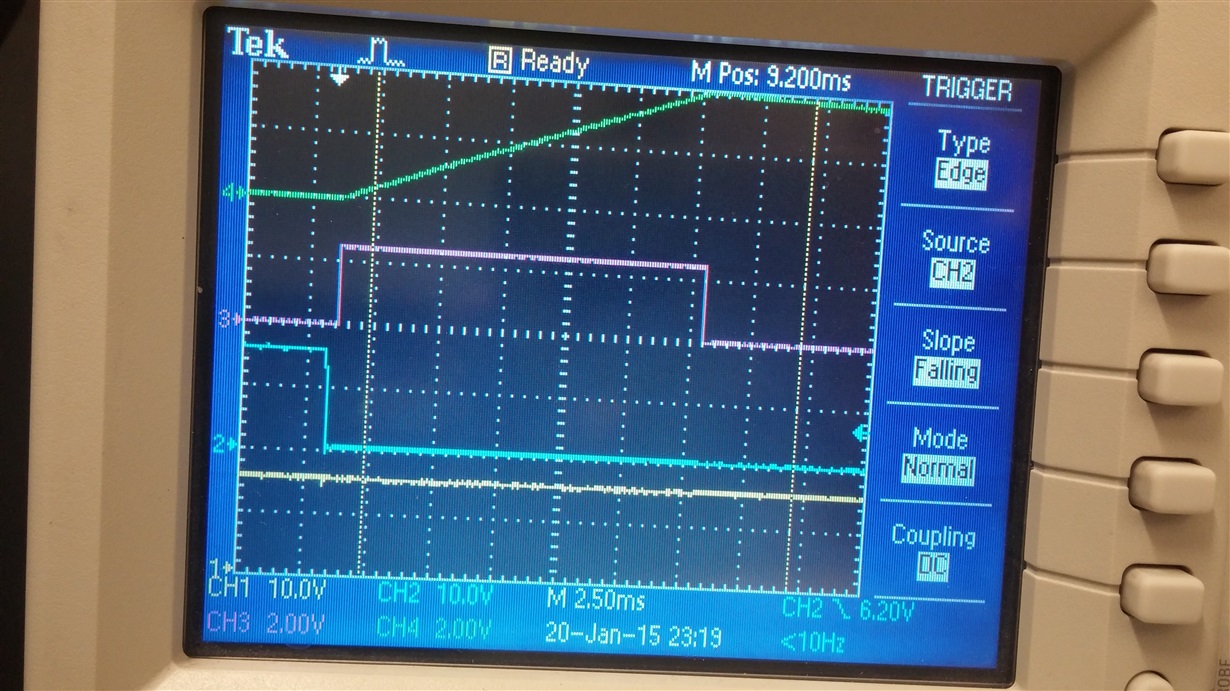

I'm using 0.1U at the timer capacitor, BSZ042N06NS for a FET and 6m Ohm for Rsh. So my current limit is 8.33A.

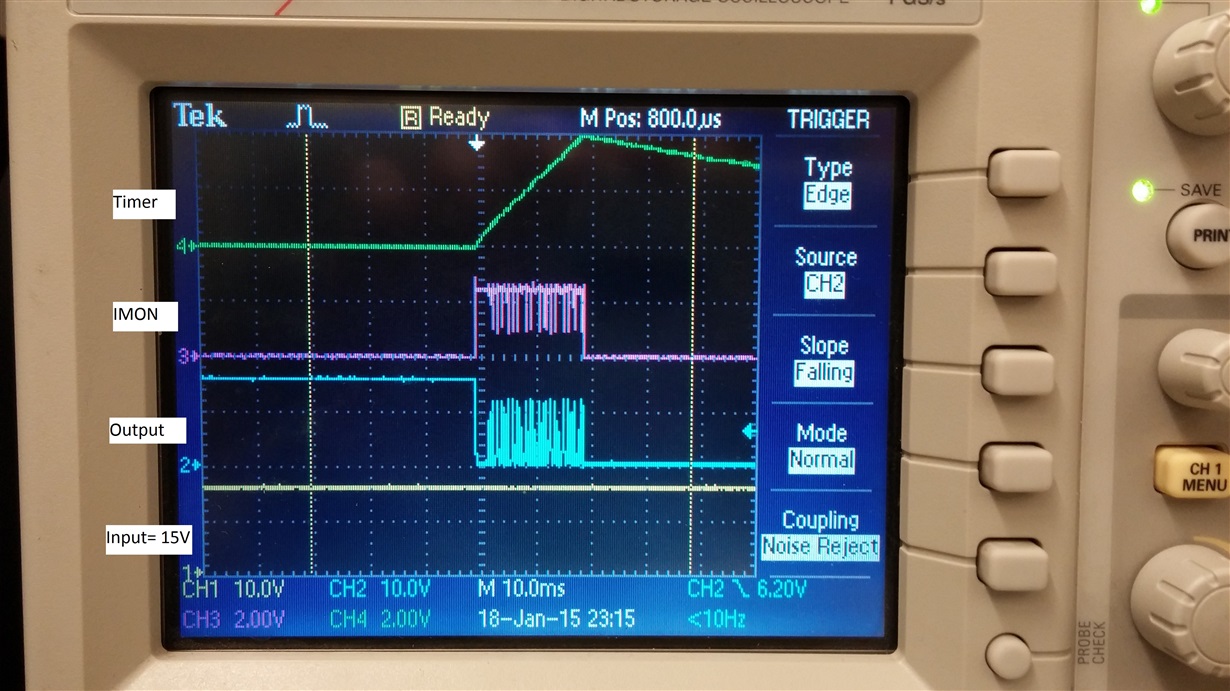

Vin=28V

No need for OV (tied to GND). UVEN pull-up of 100Kohm to VCC.

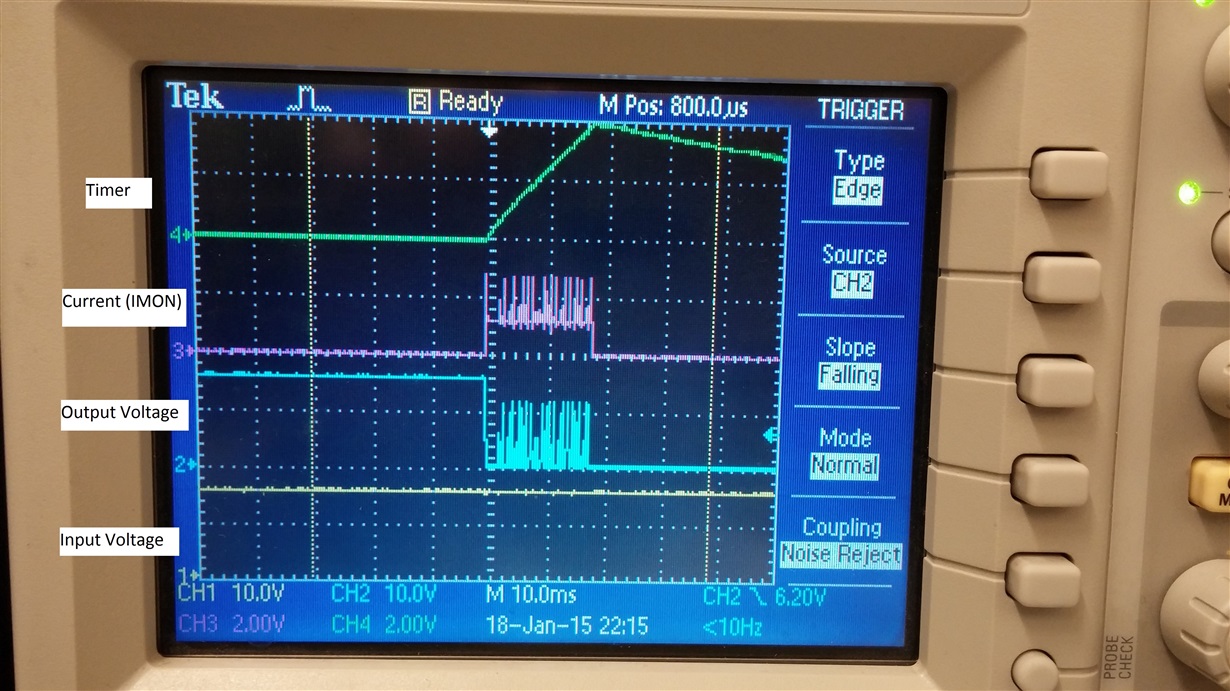

When loading the output at 10A (with electrical load at constant current mode) it burns the FET immediately.

At the Tina simulation (when using constant resistor at the output) I can see that it's limiting the power and after ~15mSec it turns off the FET. That might be the resion why my FET burned.

What can I do, so the TPS2492 will work as current limit and close the FET without limiting the power on the FET.

Thanks

Shmuel