Dear sir,

I have the circuit that followed attached schematic to design but change output cap to MLCC.

(C18 change to 100uF x3 MLCC, C19 change to 100uF x9 MLCC)

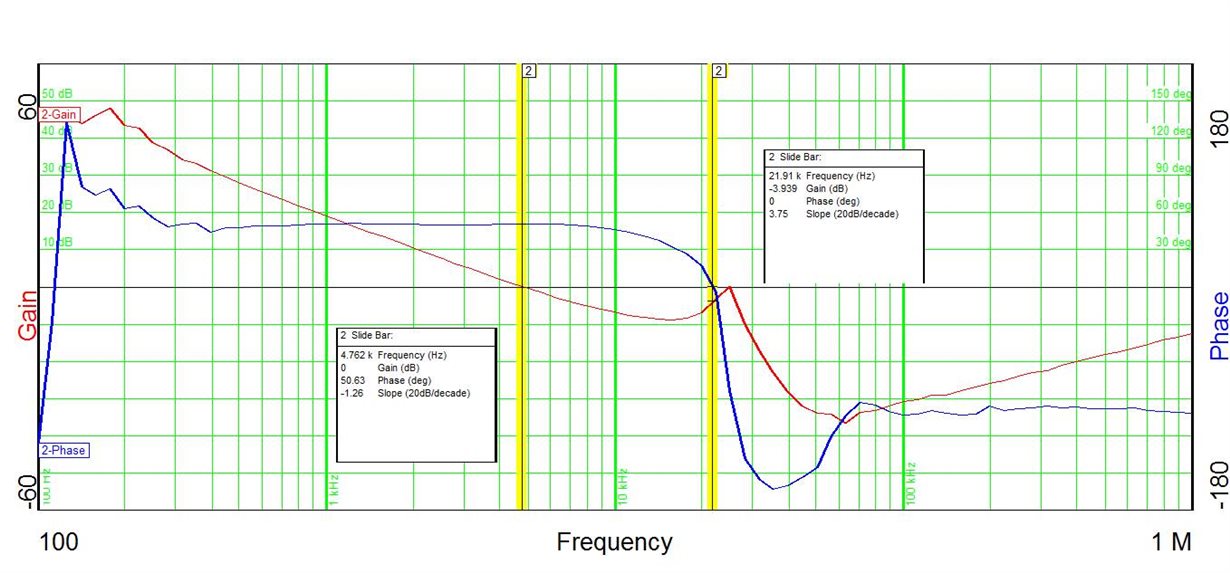

But now we can't pass bode plot gain margin to 10dB.

Would you help to provide any comments to improve bode plot? By the way, we can't use oc-con or AL-cap because this may need 7 or 8 year life cycle,

we need to keep MLCC output cap.