Hello,

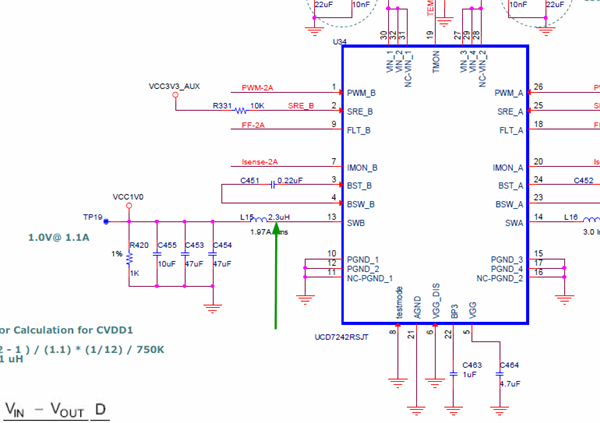

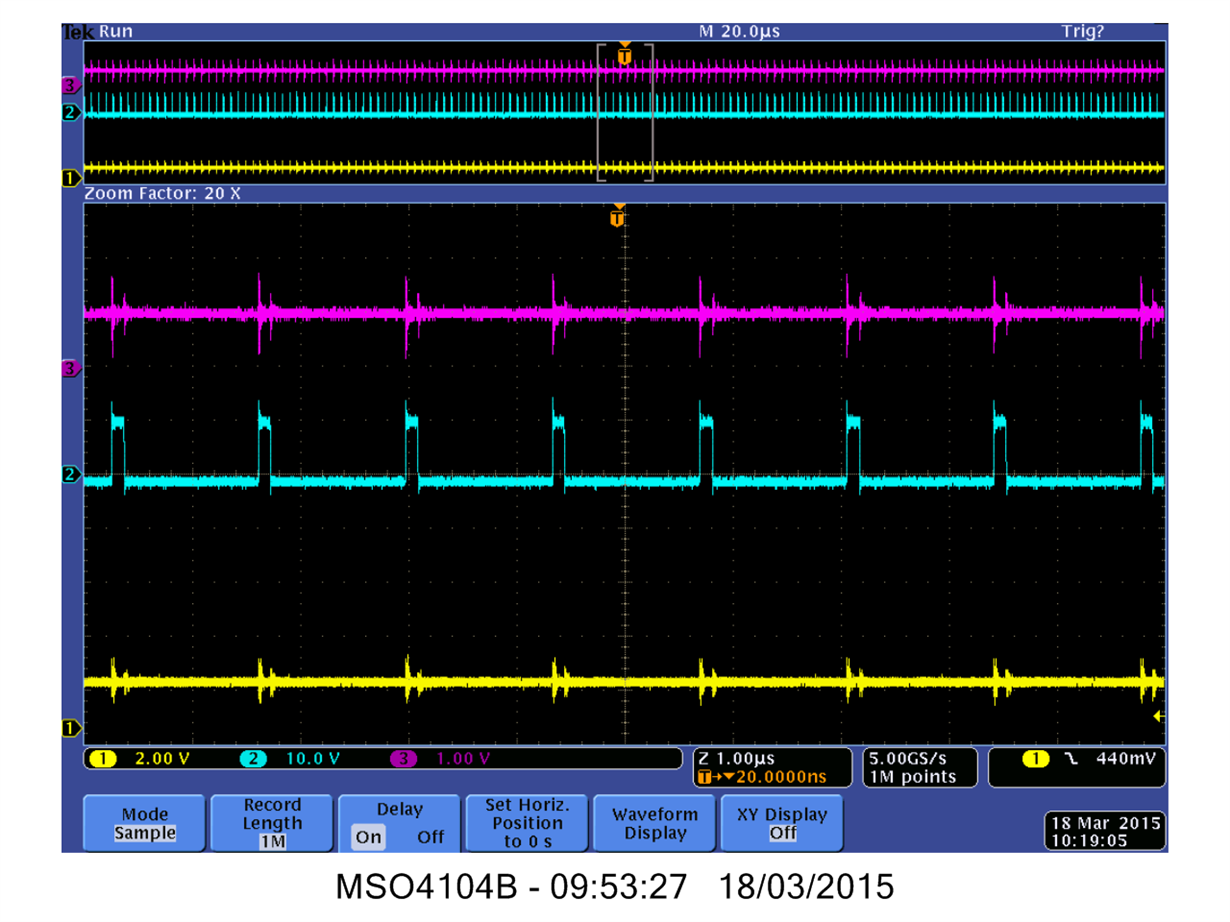

I have a C6657 evm which is misbehaving, a random time after power up (minutes to tens of minutes) the board enters an unresponsive reset state. I have tracked this down to a power supply problem: the condition is forced by an FPGA if any of the multitude of DC/DC converters on the board drop their Power good signal for longer than 0.67us (32 48MHz clocks). I have gone through all the supplies on the board and the culprit seems to be the UCD9222 that that controls two core supplies. The supplies are nominally 1V, with one being fine controlled by the DSPs VCNTL pins; this I measure as 1.1V at power on.

So, my question is, what can cause the UCD9222 to drop its PowerGood output? Is it likely that the UCD9222 device is faulty? Or could there be some other problem on the board that is causing this behaviour? Is there anything else I can check to further debug this problem?

Thanks for you help.

John Wilkes