Hi,

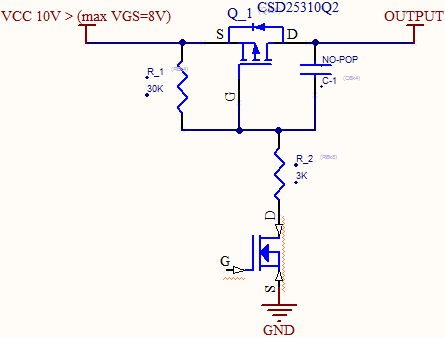

In a load supply using P-MOS(following AND9093/D), the input to source is 10V. We found unfortunately that the MOSFET (TI CSD25310Q2) we chose and soldered has only 8V maximum gate-source voltage. Although there are voltage dividers consisting of R1 and R2, we are not sure upon the sudden turning on of NMOS, whether VGS could temporarily reach 10V, and whether the P-MOSFET Q1 could stand it.

Questions:

- Could someone recommend PMOS having larger maximum VGS (hopefully > 25V which we have similar use for another higher voltage)?

- The application of using PMOS for high voltage switch should be common and VCC=10V is unlikely to be at the high end of typical applications. So how do applications typically handle voltage exceeding maximum VGS?

Matt