Hello TI and forum members! I am designing a 5V 3A power supply with the TPS62133. The most interesting charateristic of this regulator that attracted me was its high efficiency at low output currents (above around 81% @ 30mA and up to 86% @ 3A), which for higher output currents is not around the 94-96% other regulator achieve but more than doubles the maximum efficiency at very low currents when compared.

I have several questions regarding the appropiate layout of the of some traces and components:

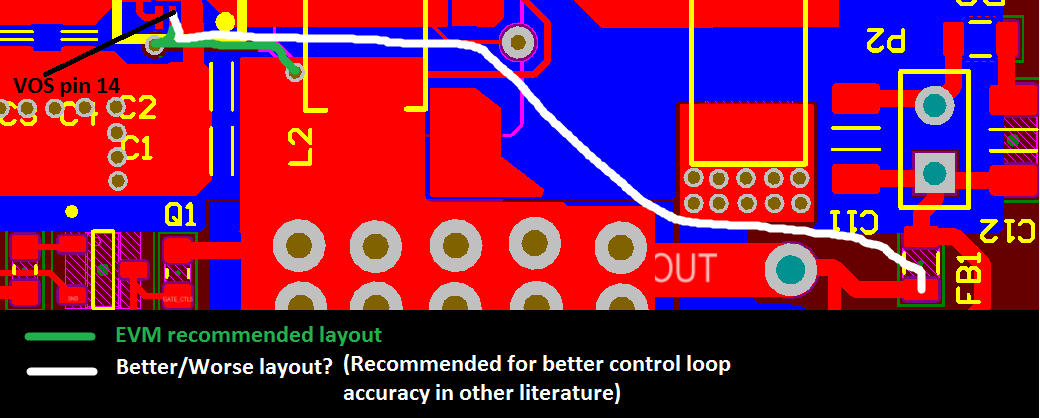

1. The VOS line in the EVM (SLVU437A) is routed from the VOS pin 14 through a via to the bottom layer, then through another via to the top layer and finally reaching VOUT just at the point where the output capacitors C3 and C4 are connected together with the inductor L2. This is not exactly the point where the load will be connected, which is the output connector J9 in the EVM. In my layout I have it routed in the same manner, not connecting the VOS pin to the point where the load will be connected but rather to exactly in the output capacitors (C2, C1) following what is stated in the datasheet and EVM. In other designs the pin that senses the voltage should be connected to the point where the load will be connected for the controller to be able to regulate the voltage at the point of interest. My question is: is the connection in the EVM good for all cases in this chip? Are there any assumptions made when making this connection at the output capacitors rather than the load? Please refer to image VOS ping routing.png

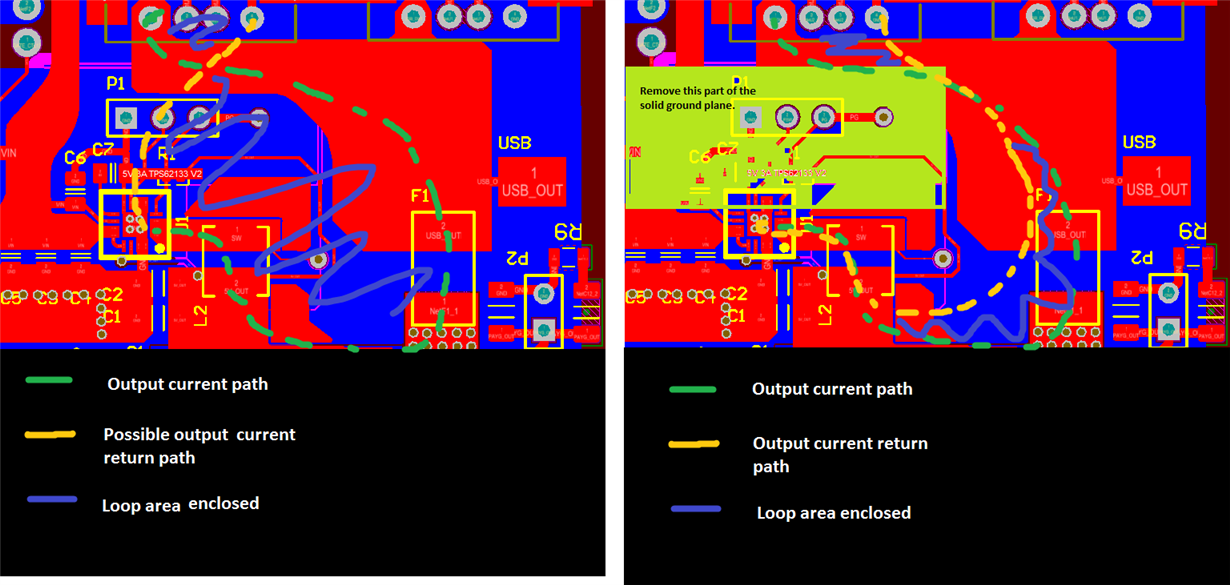

2. Loop Area for high frequency load currents: due to space/position restrictios in my application, the high frequency output load current needs to make a 90° turn near the IC. Since the radiated energy is proportional to loop area formed by the load current (as is also stated in the TPS62133 datasheet SLVSAG7C) I am not completely sure a solid ground plane would be the best low impedance/EMI Absorbing path to be used, since it would enclose a relatively large area. Instead, I was considering to route this return path just above the output current path, so that the loop area is decreased to a minimum. Would this be a better approach? or should the solid ground plane still stand despite the possible loop area? Under the understand that high frequency signals will choose the lowest impedance return path, this path would be just below the output current path, in which case the solid ground plane would be unnecessary (at least for high frequency signals). The best decision is not clear for me, so is there any recommendation? Please refer to image Return Path.png

I would greatly appreciate any feedback on this two inputs. The board was designed following as close as possible (and sometimes exactly) to the recommendations from datasheet and EVM, so I expect a first time working board within specifications.