Hi all,

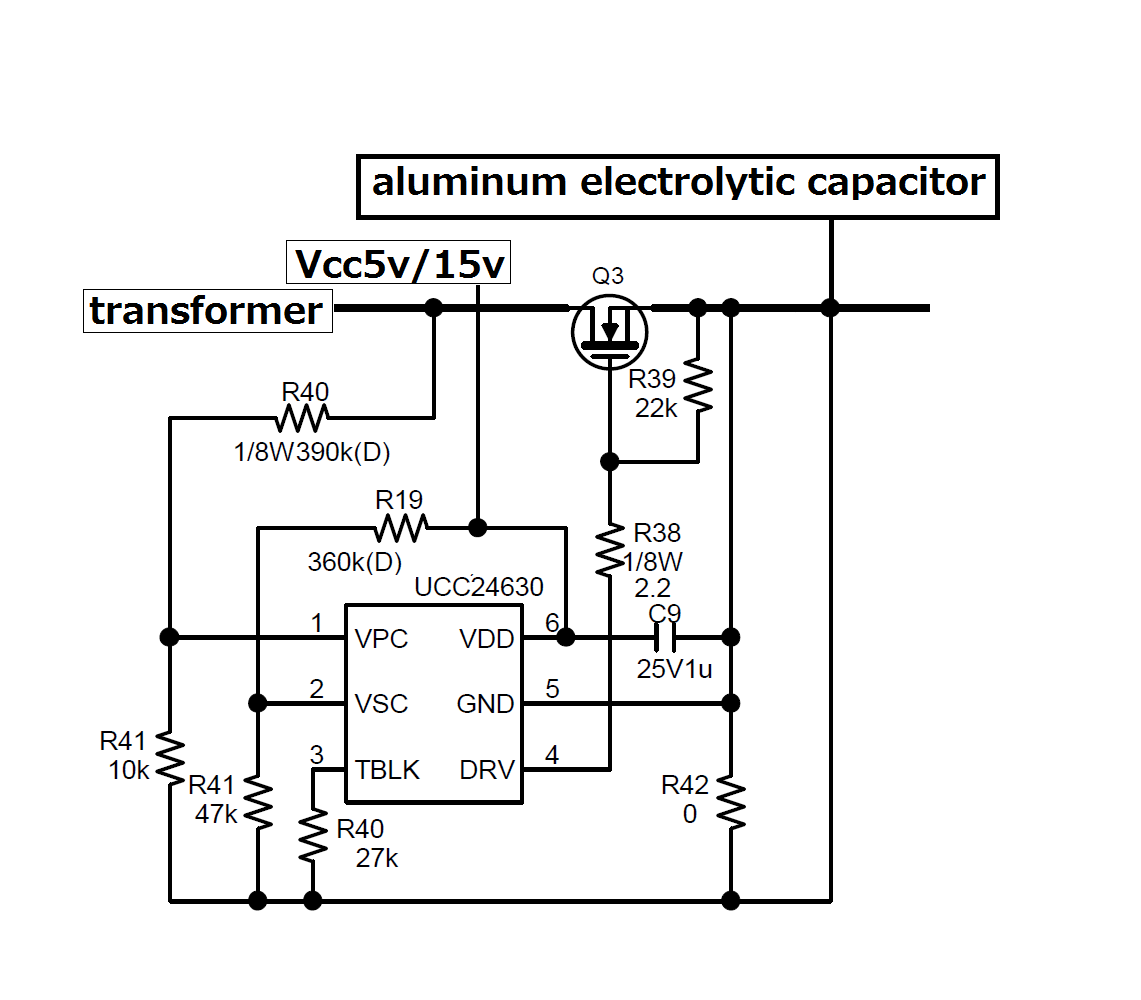

Would you mind if we ask about the high current on primary-side FET on synchronous rectification using UCC24630?

<Our recognition>

When the operation of the power supply switches from CDM operation to CCM, the high current flows the primary side FET.

We guess that turn-off delays at the secondary side FET caused it.

In this moment, due to turn-off delays at the secondary side, the primary FET and the secondary FET switch ON at the same time.

So, is our recognition correct?