Hi,

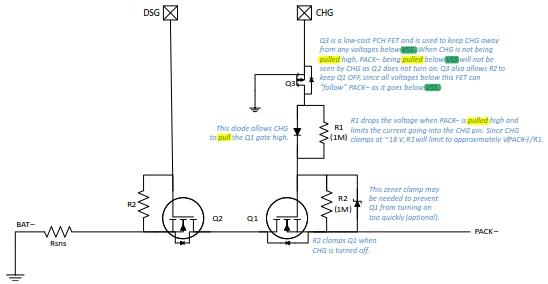

In bq769x0 and tida-00255 “pulling” is frequently assumed for where it is improbable. For example as in fig.7-3:

Q1: (PACK-) has been assumed both low and high. For proper design PACK- should the lower side of the pack and cannot be high.

The zener in parallel to 1M R2, is it for the erroneous case the PACK- is connected to HIGH of the external charger, and PACK+ to low, so opposite voltage is applied. Only in this case I saw how 1) the zener clamps voltage 2) as the side note to 1M R1 describes R1 as limit the current when PACK- pulled high.

So are they just fault-tolerant countermeasures?

Q2: (PACK-) could also be a trifle higher than VSS when discharging, but this is only due to RDSon of Q1 and Q2.

1) This should have been already considered by the designers, is it?

2) In this case even PACK- is higher than VSS, due to FET’s symmetry, Q3’s drain would be slightly higher than gate, and it is hard to say whether this marginal voltage due to (RDSon,Q1 + RDSon,Q2) can even exceed VGSth of Q3.

So I feel this case is ignorable, and the circuit as mentioned in Q1 essentially is to prevent externally applied opposite voltage.

Calino