Hi Team,

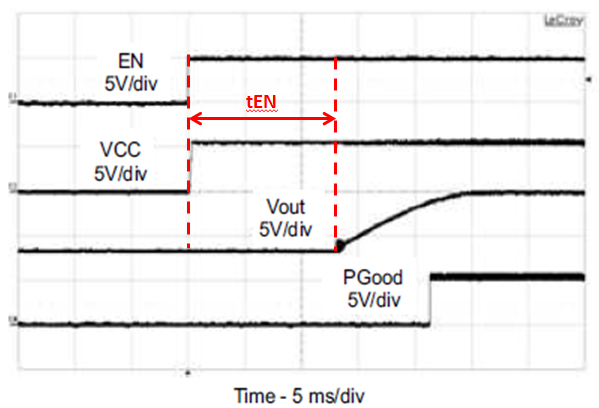

We would like to know about EN to start switching time(tEN).

-----------------------------------------------

[Q1]

I understand that “tEN” is the following figure.

Is my understanding correct?

-----------------------------------------------

[Q2]

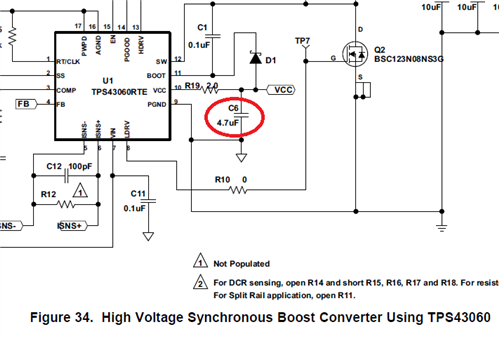

Does “tEN” depend on "Cvcc"?

If yes, could you please let us know the method of calculation of this time?

So, our customer would like to know about following contents.

-If "Cvcc" is bigger than 0.47uF, does "tEN" increase?

-If "Cvcc" is smaller than 0.47uF, does "tEN" decrease?

-Could you please let us know the max and min value of “tEN” at “Cvcc=4.7uF”.

Because, they referred to "Figure34" to design the circuit.

I would be grateful if you could reply as soon as possible.

Regards,

Kanemaru