Hi All,

Got my custom BMS PCB for a 6S battery pack from the assembly house a couple of days ago. The BMS design is based on the BQ7693000DBT AFE, BQ78350 GG and a host MCU.

After going over the datasheet and the TRM, I was unable to find a single example of an SMBUS transaction for reference, just the small timing plot.

The TRM lists with great detail the register definitions, but lacks a detailed explanation or diagram of a complete SMBUS transaction.

Currently I'm only able to get an ACK after sending the 0x16 slave address, but am clueless regarding the addressing scheme of the bq78350.

Can someone help with an SMBUS example for this device? Even a logic analyzer screenshot of a successful transaction will help.

A short explanation regarding the memory organization will truly help.

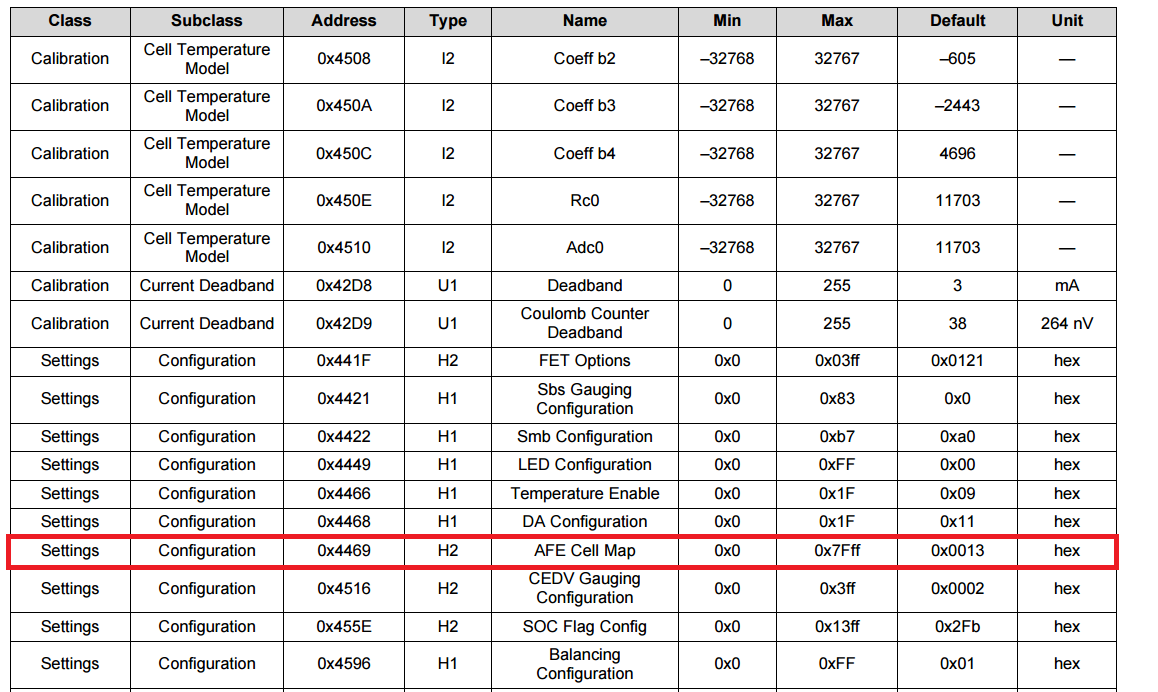

What are Class and Subclass - Base addresses?

Your kind help is much appreciated.

SBD