Hello,

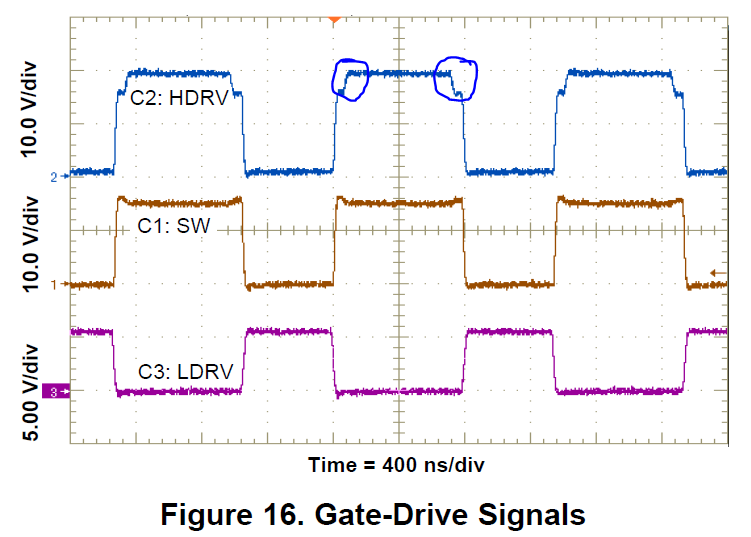

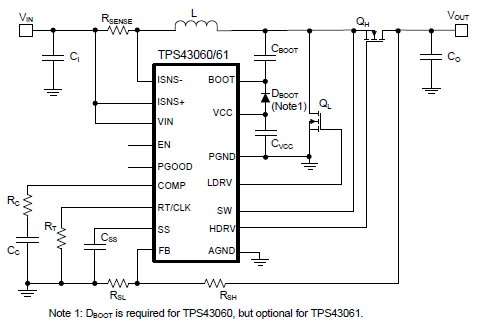

My customer is using P/N: TPS43061 boost converter as shown below. It seems like the IC or transistors continually failing. The LDRV and HDRV signals are sometimes both high simultaneously as shown in the attached screen capture (Channel 1 is HDRV and channel 2 is LDRV). Please advise.

Thanks,