Hello,

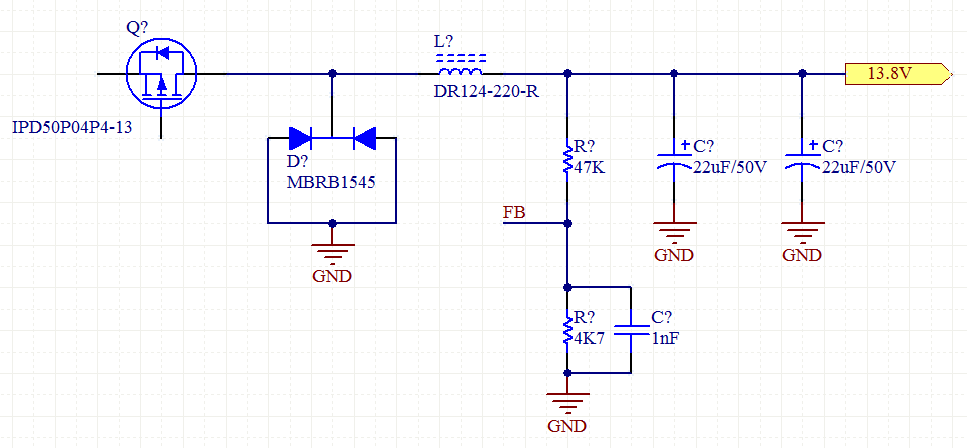

I'm working on a buck converter 24V to 12V @ 3A and I decided to test this part.

Without load, when I turn on the circuit, the output becomes in the target voltage and everything is good.

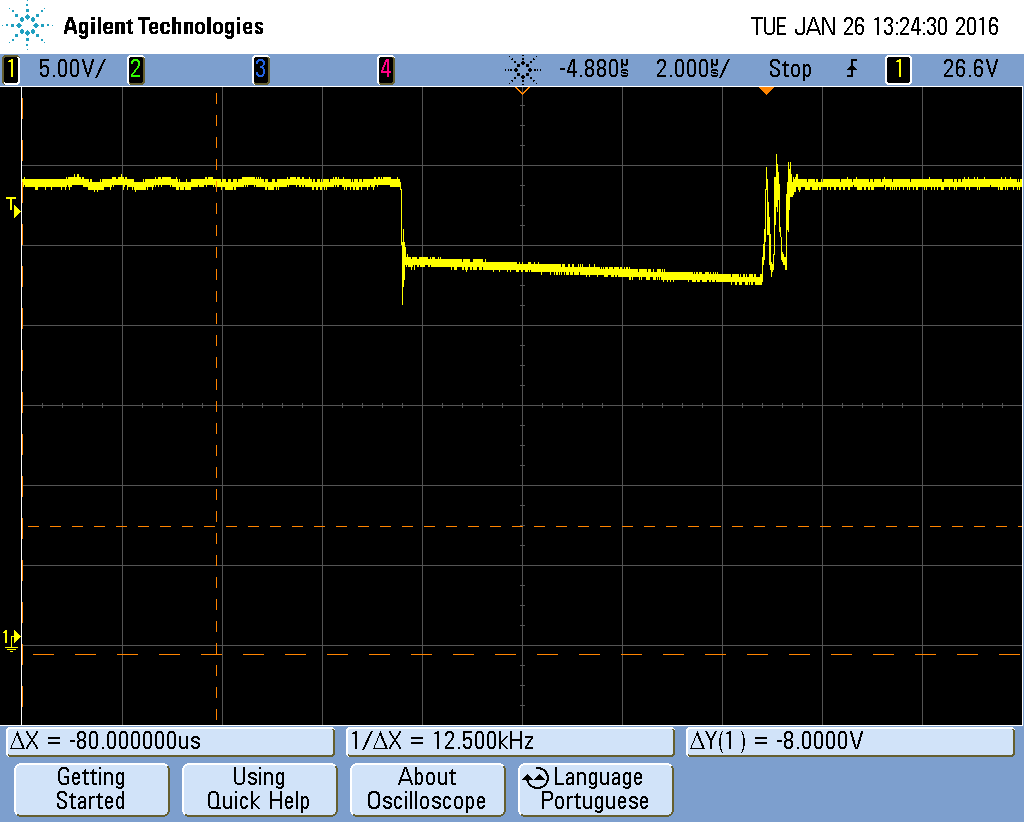

When I put any load, like for 100mA, the LM3489 heats a lot, jumps to 150 °C. The output voltage remains in the same level (12V). The only thing that I find that could heat the part would be the high frequency of switching.

I measured 1Mhz while it should be about 300 kHz using the formula (1/(2*pi*R1*CFF) = FSW/10

Why is this frequency in this high value? I tryed put it down changing the Cff but without success. I'm using 100pF now.