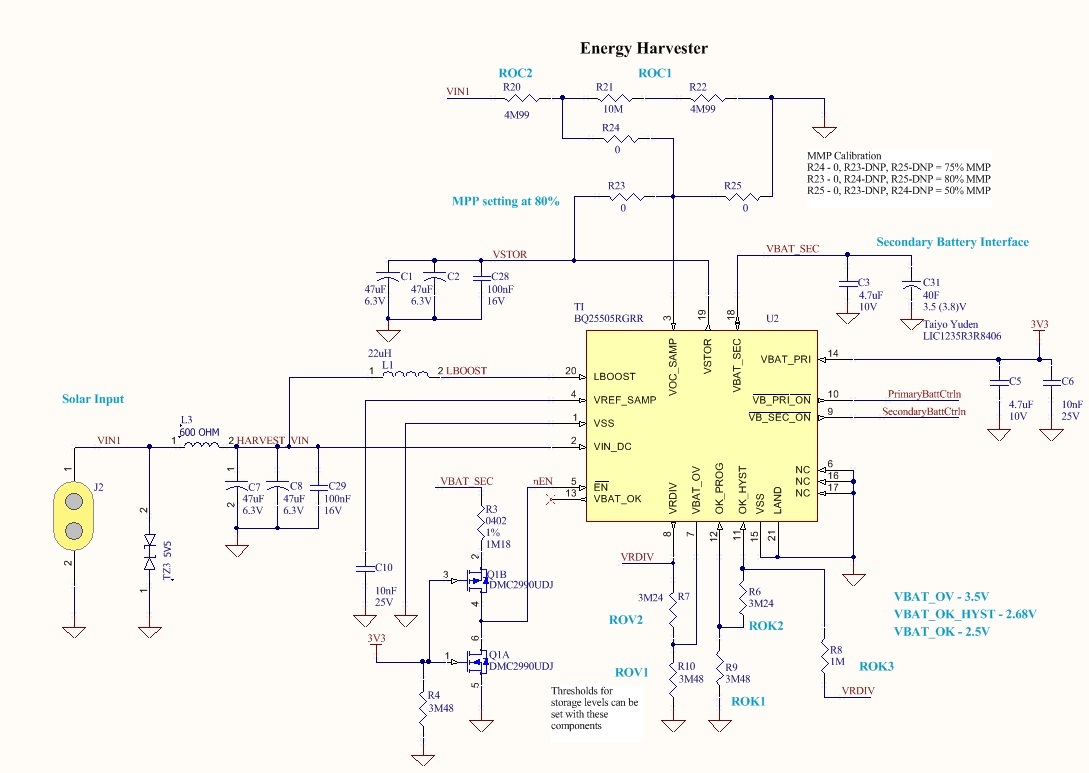

I need to minimize the current drawn from the secondary battery (a Lithium Ion Capacitor) for when my application (an energy harvesting peripheral) will be stored on a shelf before installation in order to prevent overdischarge. I want to implement a way to pull /EN high when the application is manufactured, but when it is installed onto the main product and powered, the /EN will be pulled low to turn on the charger. An easy way would be to use a large pull-up to VBAT_SEC and N_FET to VSS which is turned on when the main product is turned on. However, In order to keep /EN at a minimum of VBAT_SEC-0.2V, I need to know the input leakage of the /EN pin. If I assume it is as high as the Q-current listed (20nA), then my resistor can be no more than 8Meg. This leads to leakage of as much as 475nA when the product is powered which is a big waste of energy and may lead to overdischarge if a long period of no harvesting is encountered. I also devised a dual FET solution where I use a P-FET to isolate the pull-up when /EN is pulled low. This brings my total current to 170nA worst case. I would like to improve that if possible, but knowing the leakage into /EN over the -40C to 85C range would be a big help. Thank you for any information you can provide!

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.