Hi,

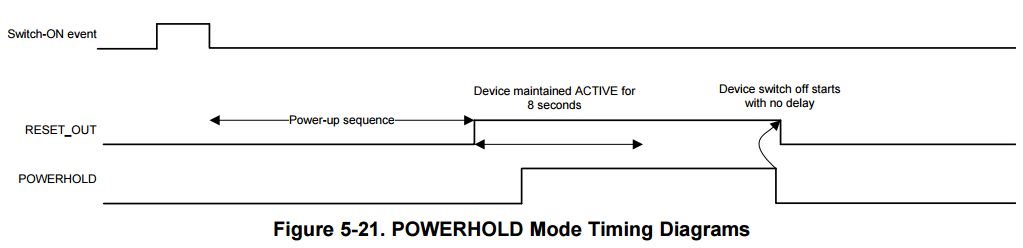

My customer plan to use POWERHOLD Mode to receipt ON request. In the Fig 5-21, the POWERHOLD signal is controlled externally, but now they plan to pull GPIO_7 pin up and hold to High level. Can you recommend this configuration?

Best Regards,

Sonoki / Japan Disty