Hi,

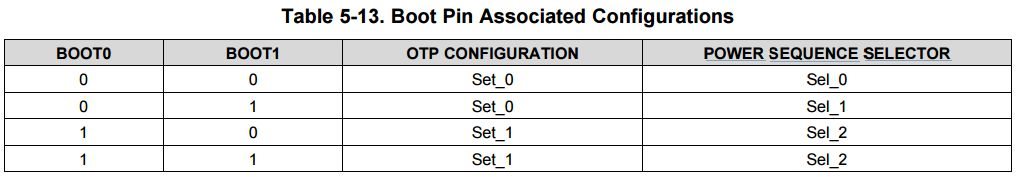

My customer is asking about POWER SEQUENCE SELECTOR. We can select three cases as Table 5-13 but I can't find the detailed explanation of Sel_0, Sel_1 and Sel_2. So can you let me know which document we should refer?

Best Regards,

Sonoki / Japan Disty