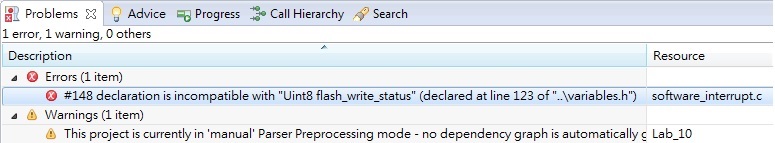

I UCD3138 trainee. When compiler finish, show "delclaration is incompatible with "Uint8 flash_write_status" at variables.h".

but I don't now how to debug. Please help me thank you all.

.

//###########################################################################

//

// FILE: software_interrupt.c

//

// TITLE: body of software interrupt routine

//

// NOTES:

// 1)

//###########################################################################

//

// Ver | dd mmm yyyy | Who | Description of changes

// ======|=============|======|==============================================

// 1.00 | 05 May 2015 | CH |

//

// Texas Instruments, Inc

// Copyright Texas Instruments 2008[Year]. All rights reserved.

//###########################################################################

#include "system_defines.h"

#include "cyclone_device.h"

#include "cyclone_defines.h"

#include "variables.h"

#include "function_definitions.h"

#include "software_interrupts.h"

#include "pmbus_common.h"

#include "pmbus_topology.h"

#if (UCD3138 | UCD3138A)

#define program_flash_integrity_word (*((volatile unsigned long *) 0x7ffc))

#endif

#if (UCD3138128 | UCD3138128A | UCD3138A64 | UCD3138A64A)

#define program_flash_integrity_word_0 (*((volatile unsigned long *) 0x7ffc))

#define program_flash_integrity_word_1 (*((volatile unsigned long *) 0xfffc))

#define program_flash_integrity_word_2 (*((volatile unsigned long *) 0x17ffc))

#define program_flash_integrity_word_3 (*((volatile unsigned long *) 0x1fffc))

#endif

unsigned int flash_write_status;

extern void zero_out_integrity_word(void);

// used to locate functions in PFLASH that will are copied to RAM and then executed from RAM

extern Uint32 zero_out_integrity_word_start[SIZE_RAM_PGM_AREA];

#pragma INTERRUPT(software_interrupt,SWI)

void software_interrupt(Uint32 arg1, Uint32 arg2, Uint32 arg3, Uint8 swi_number)

{

//make sure interrupts are disabled

asm(" MRS r4, cpsr "); // get psr

asm(" ORR r4, r4, #0xc0 "); // set interrupt disables

asm(" MSR cpsr_cf, r4"); // restore psr

switch (swi_number) //handle flash write/erase and ROM backdoor first

{

case 0:

//--------------------------------------------------------------------------------------

// SWI ALIAS: erase_data_flash_segment()

// Erases one segment of Data Flash and wait for erase to complete.

//--------------------------------------------------------------------------------------

case 1:

//--------------------------------------------------------------------------------------

// SWI ALIAS: erase_dflash_segment_no_delay()

// Erase one segment of Data Flash and return without waiting for completion.

//--------------------------------------------------------------------------------------

{

union DFLASHCTRL_REG dflashctrl_shadow; // Shadow copy of control register

if (arg1 >= DATA_FLASH_NUM_SEGMENTS)

{

return; // Invalid segment number

}

DecRegs.FLASHILOCK.all = 0x42DC157E; //unlock flash write;

// Set the bits in the Data Flash Control Register to erase the indicated segment

dflashctrl_shadow.all = DecRegs.DFLASHCTRL.all; // Read the hardware register

dflashctrl_shadow.bit.PAGE_ERASE = 1; // Erase one segment

dflashctrl_shadow.bit.PAGE_SEL = arg1; // Segment number

DecRegs.DFLASHCTRL.all = dflashctrl_shadow.all; // Write the hardware register

if (swi_number == 1) // 0= Wait for erase to complete, 1= return immediately

{

return;

}

while(DecRegs.DFLASHCTRL.bit.BUSY != 0)

{

; //do nothing while it programs

}

return;

}

case 3: //write word to data flash

// if(((arg1) < DATA_FLASH_START_ADDRESS) || ((arg1) > DATA_FLASH_END_ADDRESS))

// { //if out of data flash range

// return;

// }

//this clears read only bit to permit writes to data flash.

// DecRegs.FLASHILOCK.all = 0x42DC157E; //unlock flash write

//#ifdef UCD3138

// DecRegs.MFBALR2.bit.BLOCK_SIZE =2;

// DecRegs.MFBALR2.bit.ADDRESS = 0x22;

//#elif UCD3138128

//#elif UCD3138064

//#elif UCD3138A64

//#endif

// DecRegs.MFBALR2.bit.RONLY = 0;

//put data in word.

// *(Uint32 *)(arg1 & 0xfffffffc) = arg2 ;

// DecRegs.MFBALR2.bit.RONLY = 1;

// while(DecRegs.DFLASHCTRL.bit.BUSY != 0)

// {

// ; //do nothing while it programs

// }

return;

//handle interrupt enables/disables next

case 4: //enable fiq

asm(" MRS r0, spsr "); //get saved psr

asm(" BIC r0, r0, #0x40 "); // clear fiq disable

asm(" MSR spsr_cf, r0"); //restore saved psr

return;

case 5: //disable fiq

asm(" MRS r0, spsr "); //get saved psr

asm(" ORR r0, r0, #0x40 "); // set fiq disable

asm(" MSR spsr_cf, r0"); //restore saved psr

return;

case 6: //enable irq

asm(" MRS r0, spsr "); //get saved psr

asm(" BIC r0, r0, #0x80 "); // clear irq disable

asm(" MSR spsr_cf, r0"); //restore saved psr

return;

case 7: //disable irq

asm(" MRS r0, spsr "); //get saved psr

asm(" ORR r0, r0, #0x80 "); // set irq disable

asm(" MSR spsr_cf, r0"); //restore saved psr

return;

case 8: //write to fiq/irq program_control_register

CimRegs.FIRQPR.all = arg1;

return;

case 9: //write to fiq/irq program_control_register

CimRegs.REQMASK.all = arg1;

return;

case 10: // switch to supervisor mode

asm(" MRS r0, spsr "); //get saved psr

asm(" BIC r0, r0, #0x1F "); // clear 5 lsbs.

asm(" ORR r0, r0, #0x13 "); // set mode bits to 13.

asm(" MSR spsr_cf, r0"); //restore saved psr

return;

case 11: // switch to user mode

asm(" MRS r0, spsr "); //get saved psr

asm(" BIC r0, r0, #0x1F "); // clear 5 lsbs.

asm(" ORR r0, r0, #0x10 "); // set mode bits to 10.

asm(" MSR spsr_cf, r0"); //restore saved psr

return;

case 12: // clear integrity word.

{

register Uint32 * program_index = (Uint32 *) 0x19000; //store destination address for program

register Uint32 * source_index = (Uint32 *)zero_out_integrity_word; //Set source address of PFLASH;

register Uint32 counter;

for(counter=0; counter < 32; counter++) //Copy program from PFLASH to RAM

{

*(program_index++)=*(source_index++);

}

}

{

register FUNC_PTR func_ptr;

func_ptr=(FUNC_PTR)0x19000; //Set function to 0x19000

func_ptr();

DecRegs.MFBALR1.bit.RONLY = 1; //restore it to read only

DecRegs.MFBALR17.bit.RONLY = 1; //restore it to read only

SysRegs.SYSECR.bit.RESET= 2; //reset device

//////////////////////////以下原本////////////////////////////////

// register Uint32 * program_index = (Uint32 *)ram_program_area; // destination

// register Uint32 * source_index = (Uint32 *)zero_out_integrity_word_start; // source address of function in PFLASH to copy to RAM

// register Uint32 counter;

// for(counter=0; counter < SIZE_RAM_PGM_AREA; counter++) // Copy program from PFLASH to RAM

// {

// *(program_index++)=*(source_index++);

// }

// Note that for UCD3138064, UCD3138A64 and UCD3138128, we're only clearing checksum in first program flash block

// for UCD3138A64 and UCD3138128, we're not even clearing the entire checksum (as it's a double word for these parts, we're just clearing the most significant word)

// This will be enough to prevent lockout though (so we'll return to ROM mode after a POR)

// zero_out_integrity_word(); // clear the integrity word

// SysRegs.SYSECR.bit.RESET = 2; // reset processor (return to ROM mode after POR)

//////////////////////////以上原本////////////////////////////////

return;

}

case 13: //write block to data flash

//--------------------------------------------------------------------------------------

// SWI ALIAS: write_data_flash_block()

// Copies a block of data from a source (typically RAM) to a destination in Data Flash.

// Handles locking and unlocking the read-only bit.

// Includes necessary delays while writing.

// Assumptions:

// Destination address is in Data Flash.

// Destination addresses start and end on word boundary.

// Source addresses start and end on word boundaries.

//--------------------------------------------------------------------------------------

{

volatile Uint32* dest_ptr = (volatile Uint32*)(arg1 & 0xfffffffc);

Uint32* src_ptr = (Uint32*)(arg2);

int32 byte_counter = (int32)arg3; // Use int instead of Uint in case count is not a multiple of 4

// Validate that destination address is in Data Flash

if( ((arg1) < DATA_FLASH_START_ADDRESS)

||((arg1) > DATA_FLASH_END_ADDRESS) )

{//if out of data flash range

flash_write_status = FLASH_INVALID_ADDRESS;

return; // Return without writing to DFlash

}

// Clear read-only bit to allow writes to Data Flash.

DecRegs.MFBALR2.bit.RONLY = 0;

// Copy a block of RAM to DFlash

while (byte_counter > 0)

{

Uint32 temp_word = *src_ptr++;

DecRegs.FLASHILOCK.all = 0x42DC157E; //unlock flash write

// Write the temp word to DFlash.

*dest_ptr = temp_word;

// *** Should add value to checksum.

// checksum += temp.word;

// Wait for any previous writes to complete.

while(DecRegs.DFLASHCTRL.bit.BUSY != 0)

{

; //do nothing while it programs

}

// Read back value from DFlash. Abort if it does not match intended value.

if (*dest_ptr != temp_word)

{

// Set an error flag to indicate write failure.

flash_write_status = FLASH_MISCOMPARE;

return;

}

dest_ptr++;

byte_counter -= 4;

}

// Set read-only bit to protect Data Flash

DecRegs.MFBALR2.bit.RONLY = 1;

flash_write_status = FLASH_SUCCESS;

return;

}

case 14: // erase entire Program Flash

{

{

#if (UCD3138 | UCD3138A)

register Uint32 * program_index = (Uint32 *) 0x19000; //store destination address for program

register Uint32 * source_index = (Uint32 *)clear_program_flash; //Set source address of PFLASH;

#elif ( UCD3138064 | UCD3138064A)

register Uint32 * program_index = (Uint32 *) 0x69000; //store destination address for program

register Uint32 * source_index = (Uint32 *)clear_program_flash_1; //Set source address of PFLASH;

#elif ( UCD3138128 | UCD3138128A)

register Uint32 * program_index = (Uint32 *) 0x6a000; //store destination address for program

register Uint32 * source_index = (Uint32 *)clear_program_flash_0; //Set source address of PFLASH;

#elif ( UCD3138A64 | UCD3138A64A)

register Uint32 * program_index = (Uint32 *) 0x6a000; //store destination address for program

register Uint32 * source_index = (Uint32 *)clear_program_flash_0; //Set source address of PFLASH;

#endif

register Uint32 counter;

for(counter=0; counter < 500; counter++) //Copy program from PFLASH to RAM

{

*(program_index++)=*(source_index++);

}

}

{

register FUNC_PTR func_ptr;

#if (UCD3138 | UCD3138A)

func_ptr=(FUNC_PTR)0x19000; //Set function to 0x19000

func_ptr();

func_ptr=(FUNC_PTR)0x70000;

#elif ( UCD3138128 | UCD3138128A)

func_ptr=(FUNC_PTR)0x6a000; //Set function to 0x6a000

#elif ( UCD3138064 | UCD3138064A)

func_ptr=(FUNC_PTR)0x69000;

#elif ( UCD3138A64 | UCD3138A64A)

func_ptr=(FUNC_PTR)0x6a000;

#endif

func_ptr();

} //execute mass erase PFLASH

return;

}

default:

break;

}

}

#ifdef MAIN // If it is the main routine

#define EXTERN // If it isn't extern, so define it as nothing

#else // If it isn't the main routine

#define EXTERN extern // If it is extern

#endif

typedef void (*FUNC_PTR)(); //used for zeroing instruction word.

//EXTERN char A_string[20]; //string variable make it a capital A so it will be first on the memory debugger list

//////////////////////////////以下新增//////////////////////////////////////////////

EXTERN Uint32 program_area[32];

EXTERN volatile Uint32 zoiw_address; //address to zero out integrity double word

EXTERN volatile Uint32 zoiw_flash_key; //flash key to zero out integrity double word - tells it which one to zero out.

typedef struct

{

Uint32 address; //Value from adc for device address

Uint32 vin_mon; //Value from adc for Vin

Uint32 ishare; //Value from adc for Ishare

Uint32 vo_sense; //Value from adc for Vout

Uint32 ips; //Value from adc for primary current sense

Uint32 vo_ovp; //Value from adc for Vin

Uint32 temp; //Value from adc for SR MOSFET temperature

Uint32 io_sense; //Value from adc for Iout

Uint32 device_temp; //Value from adc for internal device temperature

Uint32 ips_hr;

Uint32 address_hr;

Uint32 device_temp_hr;

Uint32 adc_scale_factor;

} ADC_VALUES_STRUCT;

struct PFC_OUT_STRUCT

{

unsigned char pfc_status0;

unsigned char pfc_status1;

unsigned int pfc_vac;

unsigned int pfc_iac;

unsigned int pfc_pin;

unsigned int pfc_pout;

unsigned int pfc_vdc_bus;

unsigned int pfc_sw_frequency;

unsigned char pfc_temperature;

};

typedef struct

{

Uint16 burst_mode_i_turn_on;

Uint16 burst_mode_i_turn_off;

int16 burst_mode_v_hys;

Uint32 burst_mode_int_jam_value;

Uint8 burst_mode_en; //ZCS feature

Uint8 burst_on; //ZCS feature

int32 vloop_filter;

int32 iloop_filter;

Uint8 cbc_enabled;

Uint8 cc_detected;

Uint8 cbc_detected;

Uint32 cbc_current_loop_integrator_jam_value;

Uint32 cbc_voltage_loop_integrator_jam_value;

Uint32 dpwm_status;

Uint32 fault_status;

Uint32 fault_status_raw;

Uint8 ll_en;

Uint8 cpcc_en;

Uint8 cbc_counter;

Uint8 cbc_max;

} FIQ_DATA;

typedef enum

{

STATE_IDLE,

STATE_CHECK_RAMP_UP,

STATE_HIGH_CURRENT_DURING_RAMP_UP,

STATE_BOUNCE_TO_RAMP_UP_AFTER_WAITING,

STATE_RAMP_UP,

STATE_RAMP_DOWN,

STATE_REGULATED,

STATE_LIGHT_LOAD,

STATE_CPCC,

STATE_FAULT,

STATE_HICCUP,

STATE_VOUT_TRANSITION,

NONE

} SUPPLY_STATE;

EXTERN FIQ_DATA fiq_data;

EXTERN Uint32 xn_bins[64]; //xn histogram bins

EXTERN int loop_counter; //Counter for tracking the number of samples to collect

EXTERN int number_of_samples; //Total number of samples to collect

EXTERN int start_monitor; //RAM variable to start xn data collection

EXTERN int ramp_complete; //Value stored in FeCtrl0Regs.RAMPSTAT.bit.RAMP_COMP_INT_STATUS

EXTERN ADC_VALUES_STRUCT adc_values; //ADC Readings

EXTERN ADC_VALUES_STRUCT adc_values_avg;//ADC Readings Averaged

EXTERN SUPPLY_STATE supply_state,supply_state_when_fault; //Supply state enum for state machine

EXTERN Uint8 uart_text_rx_buf[UART_RX_SIZE*2 + 2]; //UART receive buffer in text mode

EXTERN Uint8 uart_text_tx_buf[UART_TX_SIZE*2 + 2]; //UART transmit buffer in text mode

EXTERN Uint8 uart_rx_buf[UART_RX_SIZE]; //UART receive buffer

EXTERN Uint8 uart_tx_buf[UART_TX_SIZE]; //UART transmit buffer

EXTERN Uint8 uart_rx_data_rdy; //flag, received a new data packet

EXTERN Uint8 uart_tx_data_rdy; //flag, a new data packet is ready for transmit

EXTERN Uint8 uart_rx_buf_ptr; //point to the buffer which will store the coming byte

EXTERN Uint8 uart_tx_buf_ptr; //point to buffer whose data is going to be sent out

EXTERN Uint16 uart_rx_timeout; //count IRQ, UART receiver will start over when timeout

EXTERN Uint16 uart_tx_timeout; //count IRQ, UART needs to wait for a certain period before send the next data packet

EXTERN struct PFC_OUT_STRUCT pfc_out_struct;

EXTERN Uint8 pfc_command;//for APEC demo

EXTERN Uint8 pfc_phase_2_enable;//for APEC demo

EXTERN Uint8 pfc_zvs_enable;//for APEC demo

EXTERN Uint8 pfc_os_enable;//for APEC demo

EXTERN Uint8 llc_sr_enable;//for APEC demo

EXTERN Uint8 previous_llc_sr_command;

EXTERN Uint8 erase_segment_counter; // Number of DFlash segment remaining to be erased

EXTERN Uint8 erase_segment_number; // DFlash segment number being erased

EXTERN Uint8 flash_write_status; // Global status while attempting to write to Data Flash.

EXTERN Uint16 period;

struct qnote

{

int16 mantissa;

int16 exponent;

};

EXTERN struct qnote temp_qnote1;

EXTERN struct qnote temp_qnote_scale1;

EXTERN struct qnote adc12_vin_scaler;

EXTERN int16 temp_qnote_value1;

EXTERN Uint32 rogue_errors;

EXTERN int32 current_share_int_state;

EXTERN int32 current_share_control_effort;

EXTERN int16 current_share_kp;

EXTERN int16 current_share_ki;

EXTERN int32 error_zero;

EXTERN int32 local_error;

EXTERN int32 ishare_center_threshold;

EXTERN int32 ishare_threshold;

EXTERN int32 ishare_threshold_ms;

EXTERN int32 ishare_center_threshold_ms;

EXTERN int32 ishare_threshold_master_enable;

EXTERN int32 ishare_threshold_slave_enable;

EXTERN int32 eadc_dac_target;

EXTERN int32 eadc_dac_max;

EXTERN int32 eadc_dac_min;

EXTERN int32 master_state;

EXTERN int32 master_time_count;

EXTERN int32 master_time_limit;

EXTERN int8 enable_turn_on;

EXTERN Uint32 pnom_value;

EXTERN Uint32 cpcc_count;

EXTERN int16 fault_and_warning_delay_count;

EXTERN Uint32 cpcc_ton_fault_time_limit;

EXTERN Uint32 cs_recover_time;

EXTERN Uint32 cs_recover_time_threshold;

EXTERN Uint32 filter_recover_time_threshold;

EXTERN Uint32 filter_recover_time;

EXTERN volatile Uint32 FAULTMUXINTSTAT_value;

EXTERN union CPSTAT_REG cpstat_local;

EXTERN Uint32 restart_counter;

EXTERN Uint64 p_out;

EXTERN Uint32 v_out;

EXTERN Uint32 i_out;

EXTERN Uint32 vref;

EXTERN Uint32 vdac;

EXTERN int32 error_offset;

EXTERN Uint8 cs_int_exp;

EXTERN Uint8 filter_select;

EXTERN Uint8 filter_activate;

EXTERN int16 slope_burst_mode_exp;

EXTERN int16 slope_ioff_mode_exp;

EXTERN int32 turn_on;

EXTERN int32 turn_off;

EXTERN Uint8 table_index;

EXTERN Uint8 burst_mode_enable_flag;

EXTERN int32 ioff_value;

EXTERN Uint32 start_up_delay_over;

EXTERN Uint32 count;

EXTERN Uint32 count_end;

EXTERN Uint32 sr_on;

EXTERN int32 HWBMTHRESH_SU; //ZCS feature

EXTERN int32 HWBMTHRESH_REG; //ZCS feature

EXTERN int32 HWBMTHRESH_CCCP; //ZCS feature

EXTERN int32 DCOMP2_CNT_THRESH; //ZCS feature

EXTERN int32 DCOMP2_THRESH; //ZCS feature

EXTERN Uint32 uart_auto_cal_state,result,baud_div_value;

EXTERN int result_temp,counter;

EXTERN Uint32 r1,r2,r3,r4,r5,r6,r7,r8;

EXTERN Uint32 ttemp;

//////////////////////////////以上新增//////////////////////////////////////////////

struct ADC_CHANNEL

{

int raw;

int min;

int max;

};

struct ADC_VARIABLES

{

struct ADC_CHANNEL ad02;

struct ADC_CHANNEL ad02_avg;

struct ADC_CHANNEL ad03;

struct ADC_CHANNEL ad03_avg;

struct ADC_CHANNEL ad03b;

struct ADC_CHANNEL ad03b_avg;

struct ADC_CHANNEL ad04;

struct ADC_CHANNEL ad04_avg;

struct ADC_CHANNEL ad05;

struct ADC_CHANNEL ad05_avg;

};

EXTERN struct ADC_VARIABLES adcv;

EXTERN int adRESET_POLLING; // Set to 1 to RESET the polling averaging values.

// below required for RAM program execution area

#define SIZE_RAM_PGM_AREA 32 // max size of function in 32-bit words to be copied to RAM program area

#ifdef MAIN

#pragma DATA_SECTION(ram_program_area, ".ram_pgm_area")

Uint32 ram_program_area[SIZE_RAM_PGM_AREA]; // small RAM area for storing programs which modify program flashes

#else

extern Uint32 ram_program_area[SIZE_RAM_PGM_AREA];

#endif

// above required for RAM program execution area