Thanks in advance for any insight - I'll start with the relevant programmable settings:

- Vbat_ov - 4.149V

- Vbat_ok - 3.128V

- Vbat_ok_hyst - 3.280V

- Vbat_uv - 3.085V

I'm using a solar cell with Voc = 2.52V and Isc = 150mA (MPP 2.0V and 133mA) and a 3.7V 2200mAh Li-ion battery as the storage element. I found out after the original design of the board that BQ25504 can't source the load transients from the load over the Vstor -> Vbat FET and have instead sourced the load from Vbat using the Vbat_ok signal to control an external PFET (this is a separate issue altogether but potentially relevant).

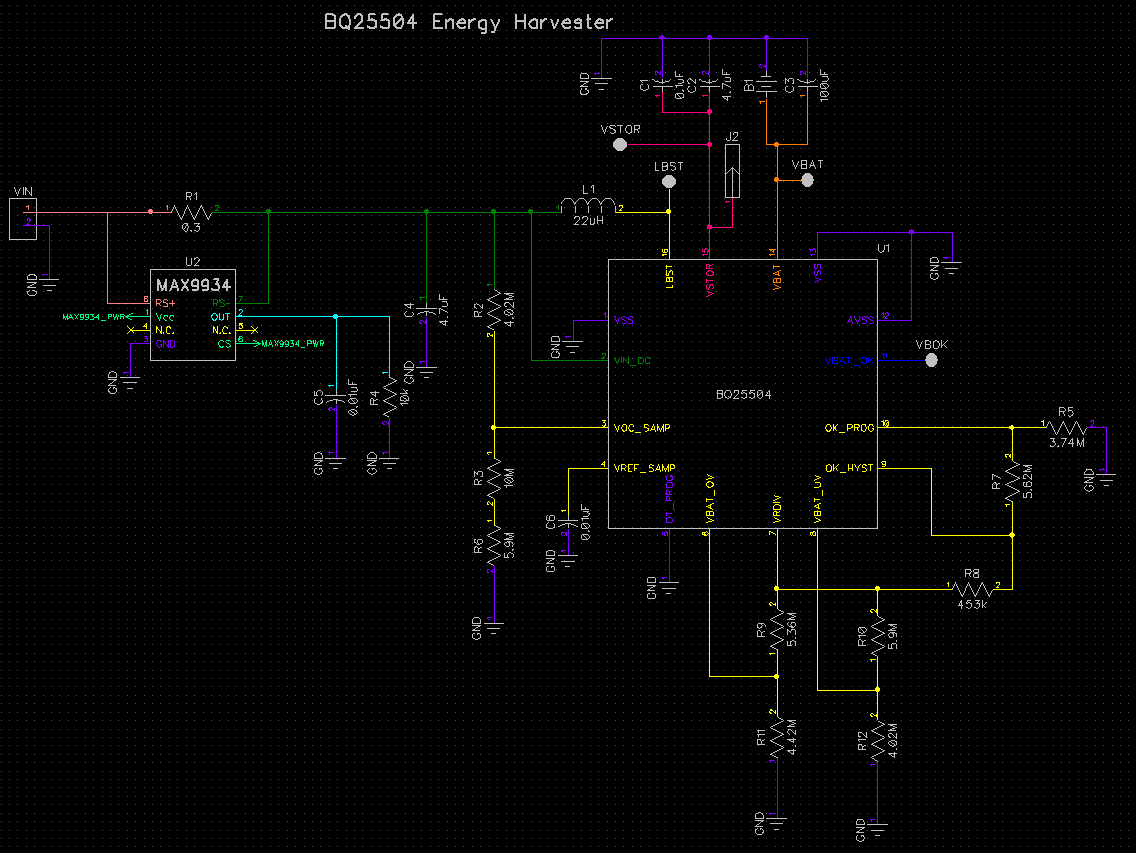

The schematic for the BQ25504 circuitry:

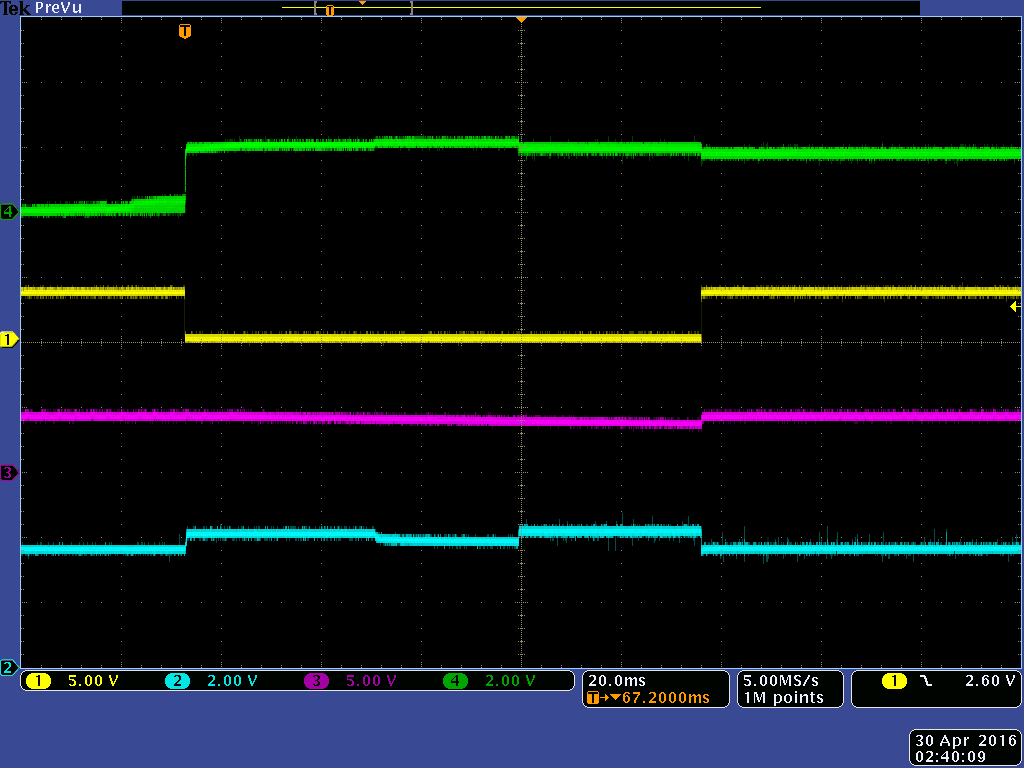

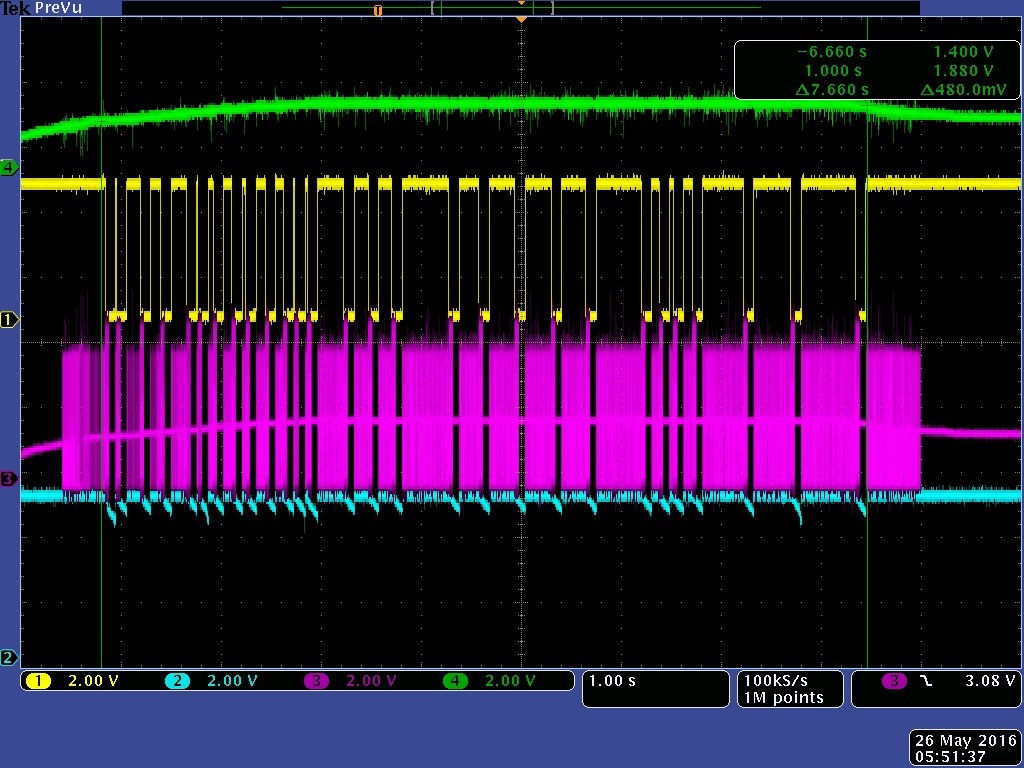

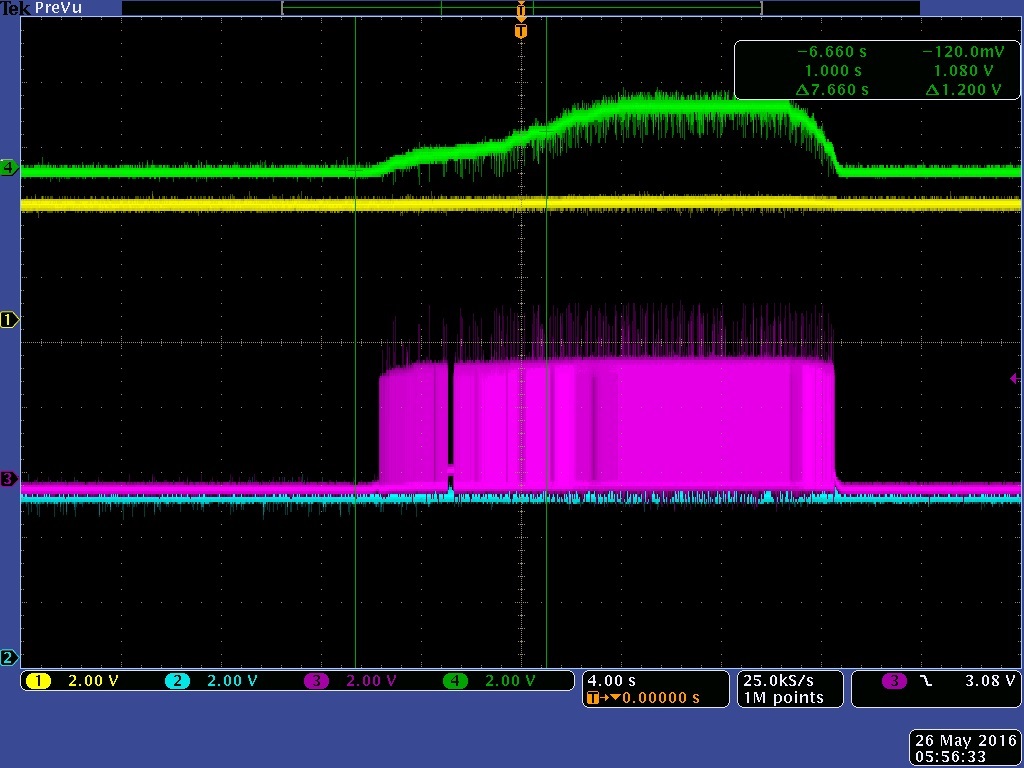

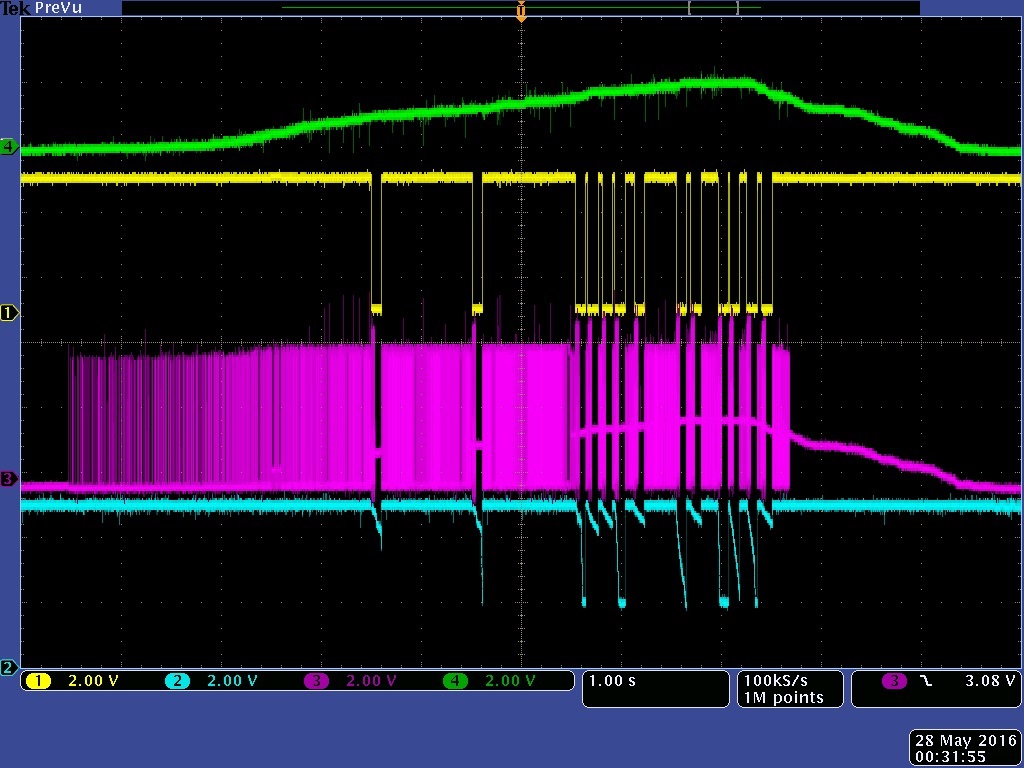

The problem I'm seeing now is that when the solar cell input varies quickly and/or drastically (e.g. a cloud moves overhead on a sunny day), I will sometimes lose power to my load. I recreated this setup in the lab and by moving an object between the light source and the solar cell I can see that the Vbat_ok line is actually dipping low although the Vbat and Vstor lines do not dip at all. I'm wondering what could possibly be causing Vbat_ok to drop low - attached is the scope output of this occurring where the scope lines are as follows:

- Vbat_ok (yellow)

- Vstor (blue)

- Load (pink)

- Vin_dc (green)

I didn't include the Vbat line on this scope but have verified that during this condition the voltage on the battery doesn't budge.

The Vbat_ok line consistently stays low for ~100ms every time this occurs. Fortunately in the lab the input capacitance on the load keeps the voltage high enough to continue operation but on my test setup that is outside I'm logging about 5-10 restarts a day where the load capacitance isn't enough to keep the load powered. Anyone have any thoughts as to how to prevent the Vbat_ok line from dipping?

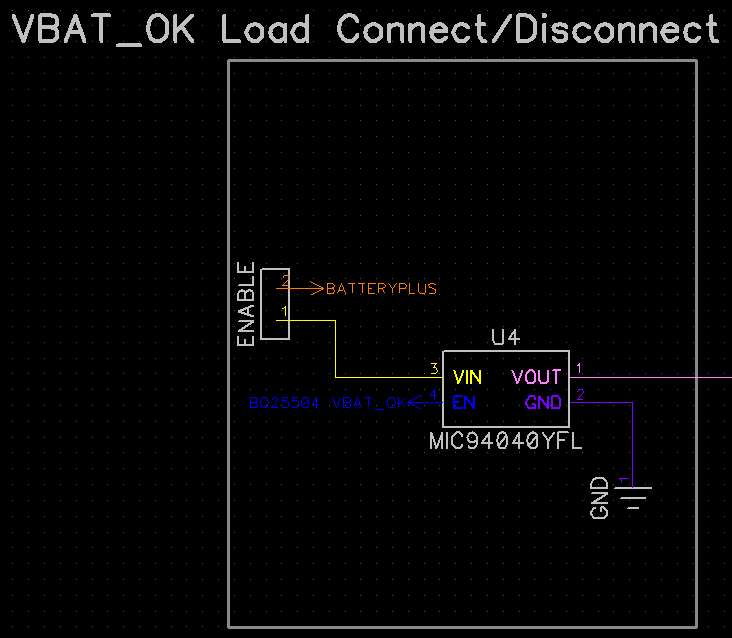

In the case it helps, here is the schematic of the external PFET:

Thanks!