Hello everyone,

I'm experiencing some trouble with TPS63020 when the input and output voltage are equals (+/-0.4V) in power save mode disabled.

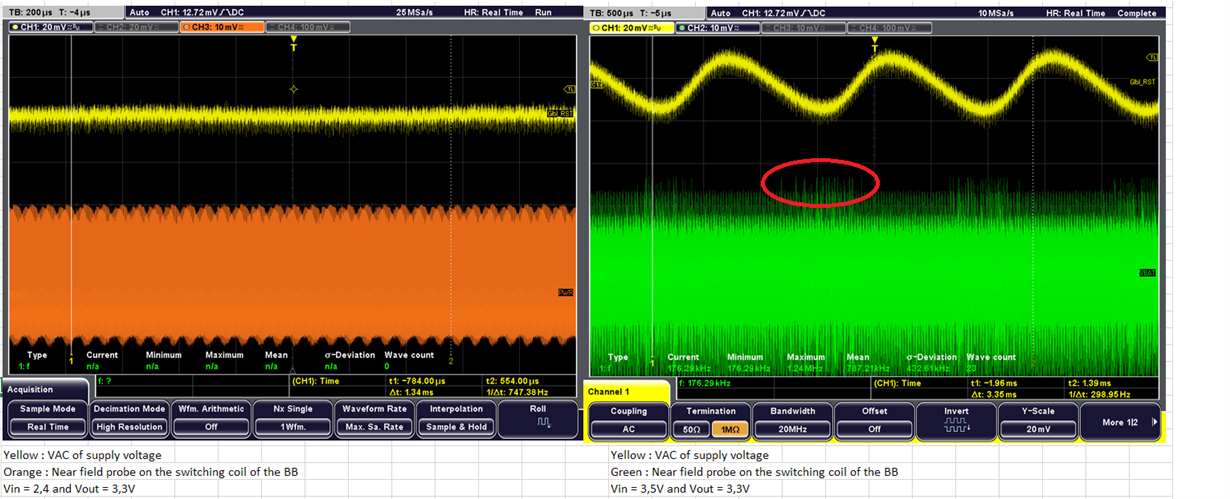

I explain : When the input and output voltage are far from each other, lets say Vin=2.4V and Vout=3.5V, then the buck boost is working nicely. But when these two voltages are close to each other then I guess the buck boost is switching between buck mode and boost mode.

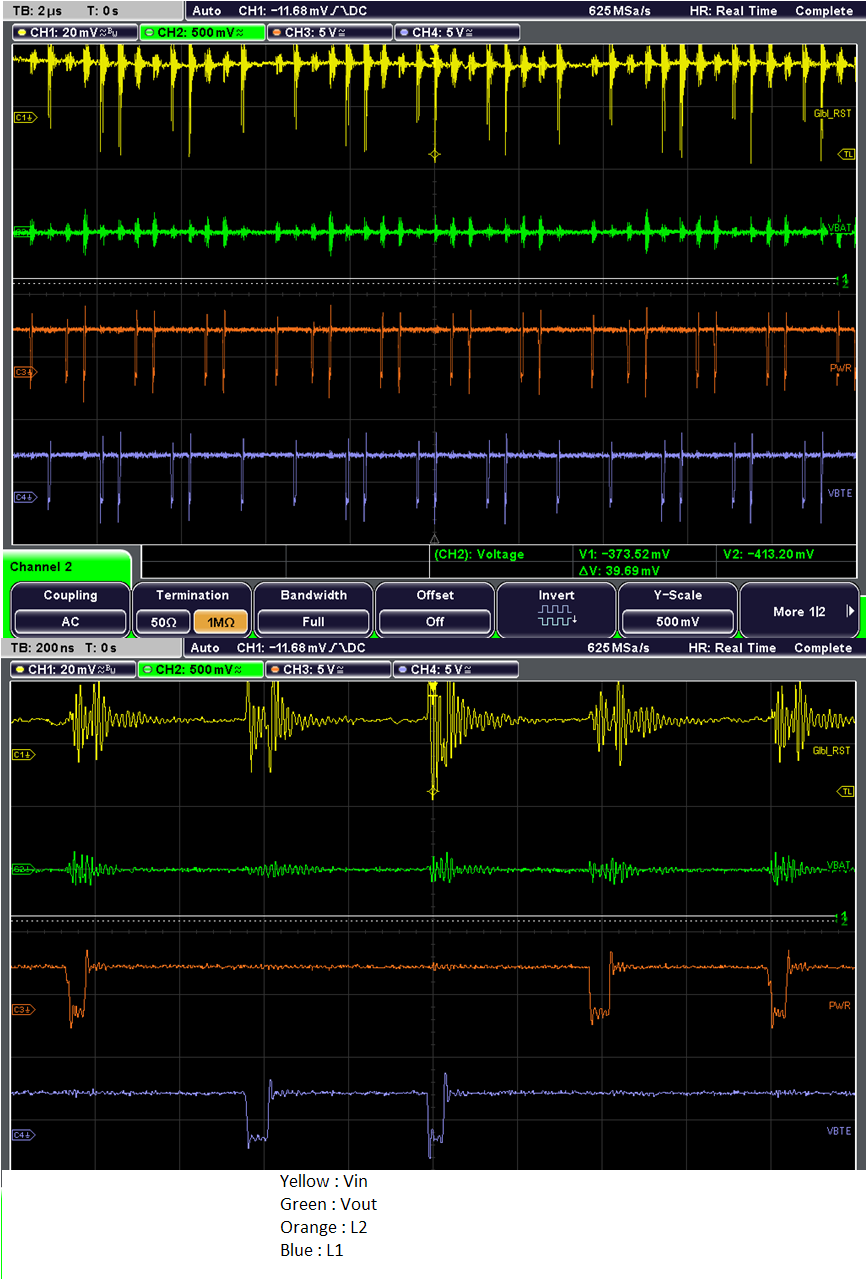

This oscillation can be seen on the input voltage : a slow ripple frequency of ~700Hz, with 30mV amplitude. When regulator switch between one mode to the other, it creates high current surges in the switching coil. These current surges create a magnetic noise that disturb a low power inductive link..

I have made some screen shots of the problem : (left is okay, right is the problem) The red circle show the repetitive magnetic noise.

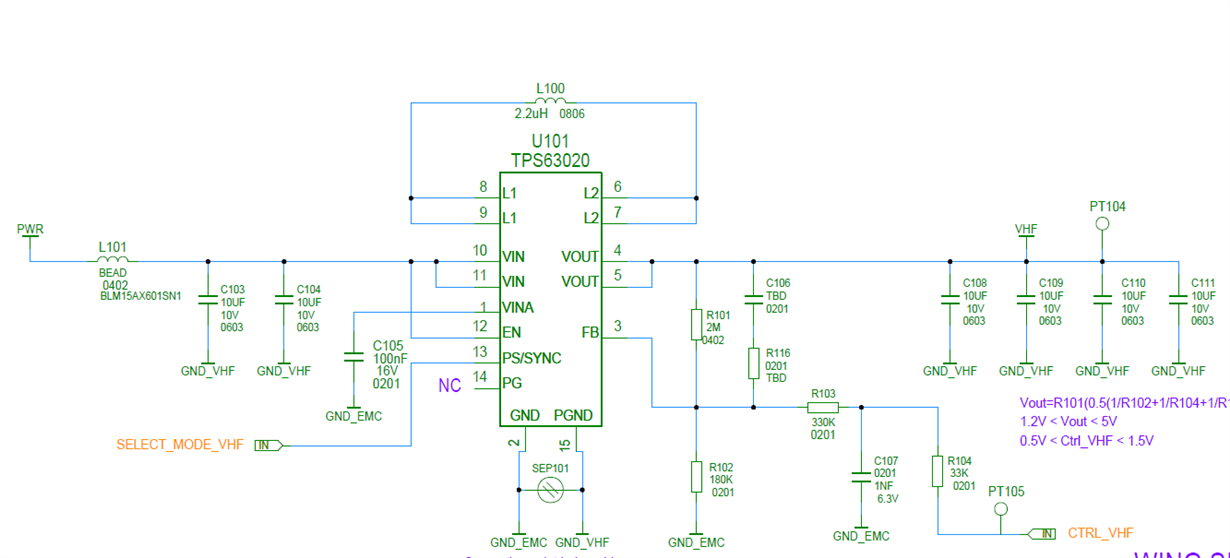

SCM and is below, I cannot show the PCB but the routing is very direct and I don't think the routing can help here.

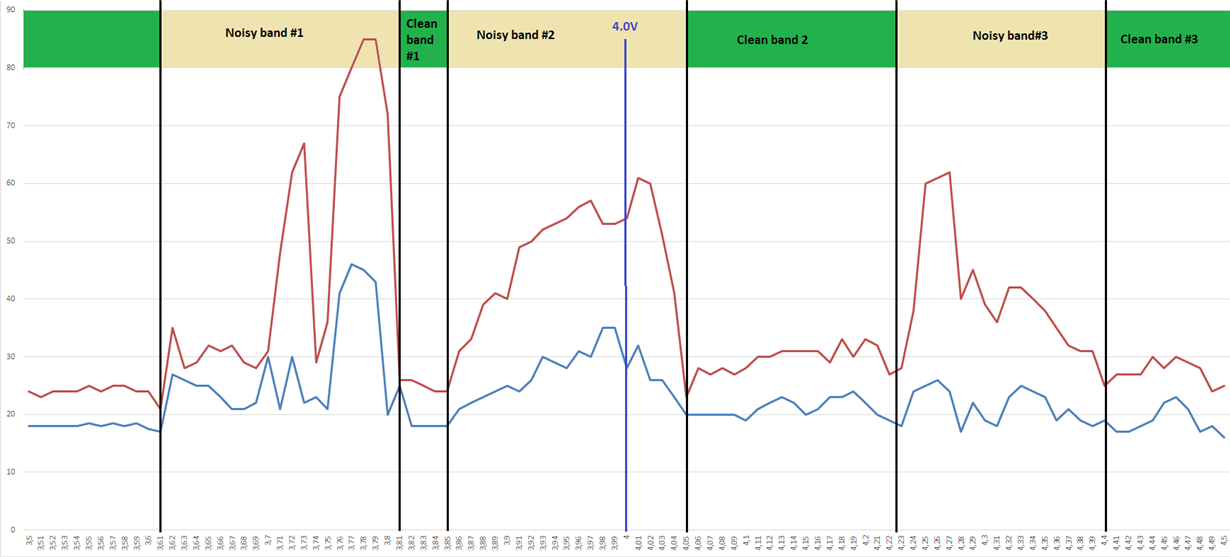

I can see this issue for a Vin=[1.8V to 4.2V] The problem is worse when Vin is high. The loads are from [10mW to 100mW].

With and without the input ferrite bead is the same, the frequency is very low anyway. I think that more decoupling at the input won't help for the same reason. There are 100µF more at the input (low ESR tantalum capacitors).

If you have any idea to reduce the impacted voltage range from +/-0.4V to +/-0.2V that would already help a lot. I wonder if we can make this problem disappear at all as this oscillation is part of the good voltage regulation of the regulator.

Any other idea? :)

Thank you in already for reading !