I am working on a 400VDC PFC input, ZVS PS FB power supply with 3.6KW output at 24V/150A.

Transformer is running at 85kHz, with turn ratio at 12:1 and Bmax at 0.22T at steady state.

A cracking noise is heard during the unit power up. Transformer saturation is observed due to magnetic flux walk away. The unit survives as CS pin comes to action.

Marking on the chip is

UCC28950

16TG4

AH6S

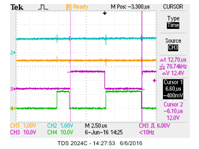

I checked the circuit at 57Vdc input voltage with synchronous rectifier disabled and output current was set at 15A. Waveforms were captured below. Figure 1 and Figure 2 shows the difference in the pulse width of OutC and OutD from UCC28950. OutC and OutD pulse will matches with each other in pulse width after start up.

How can we get rid of the uneven pulse during power up?

=================

Input Vdc 57V; Output at steady state 2.75V/15A

C1: Center tap of pwr traffo, 2nd side; C2: OutB PWM IC; C3: OutC PWM IC; C4: OutD PWM IC;

Figure 1 Figure 2

===========================================================================

C1: Center tap of pwr traffo, 2nd side; C2: CS PWM IC; C3: OutC PWM IC; C4: OutD PWM IC;

Figure 3

====================

C1: Center tap of pwr traffo, 2nd side; C2: Vo Output; C3: OutC PWM IC; C4: OutD PWM IC;

Figure 4

============