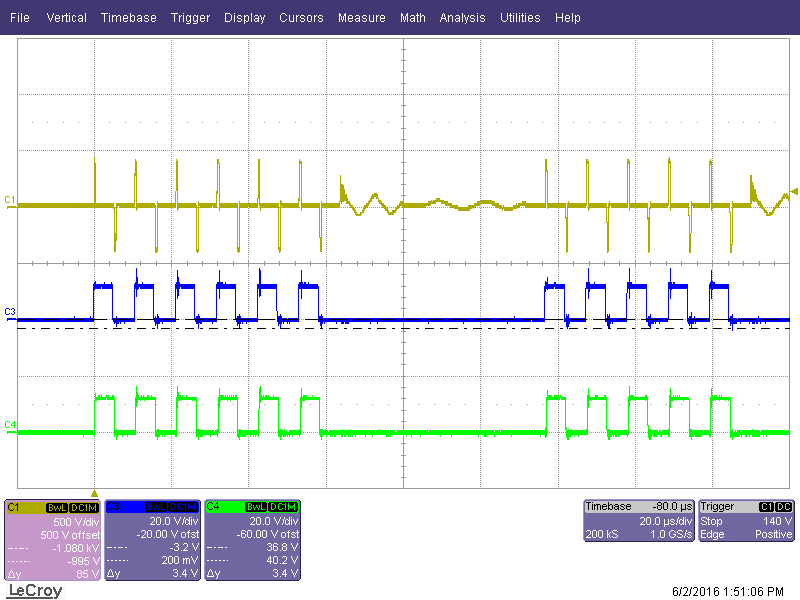

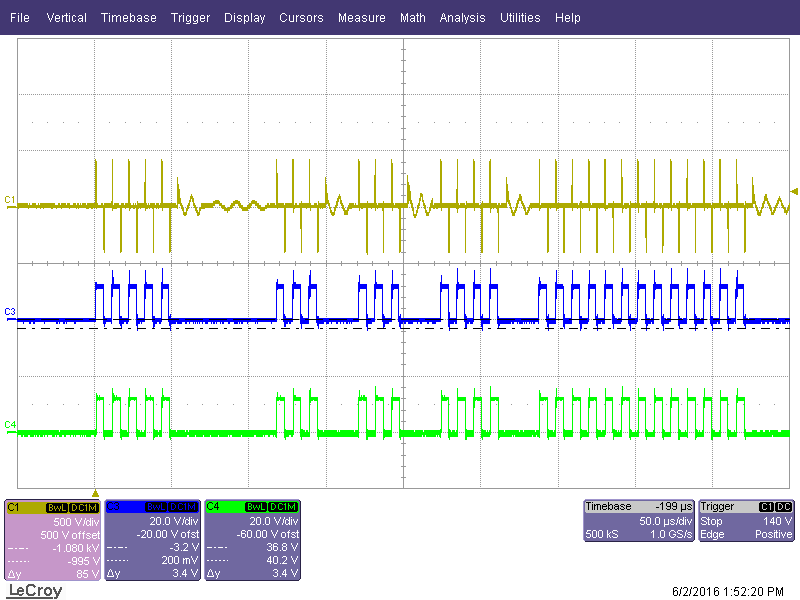

The Datasheet for the UCC28950 shows the outputs A and B, and C and D, having an uneven gate drive (two B pulse, one A pulses) on page 9. This has been confirmed by measurement on my prototype design utilising the UCC28950. One pair is always switching first and that same pair last in the pulse train. Odd switching: volt-second balance != 0

The problem is that it is driving my DC coupled gate drive transformer into saturation during burst mode and causing my gate drivers to overheat. At the moment I have not experienced any issues with my main transformer flux walking, but I probably would do with extended run times.

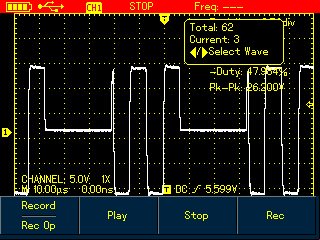

When I AC couple the GDT, the resultant offset waveform is causing the lower side active leg 'FETs to enter the linear region and they overheat.

Was it designed like this? If so, why?