Hi Sir,

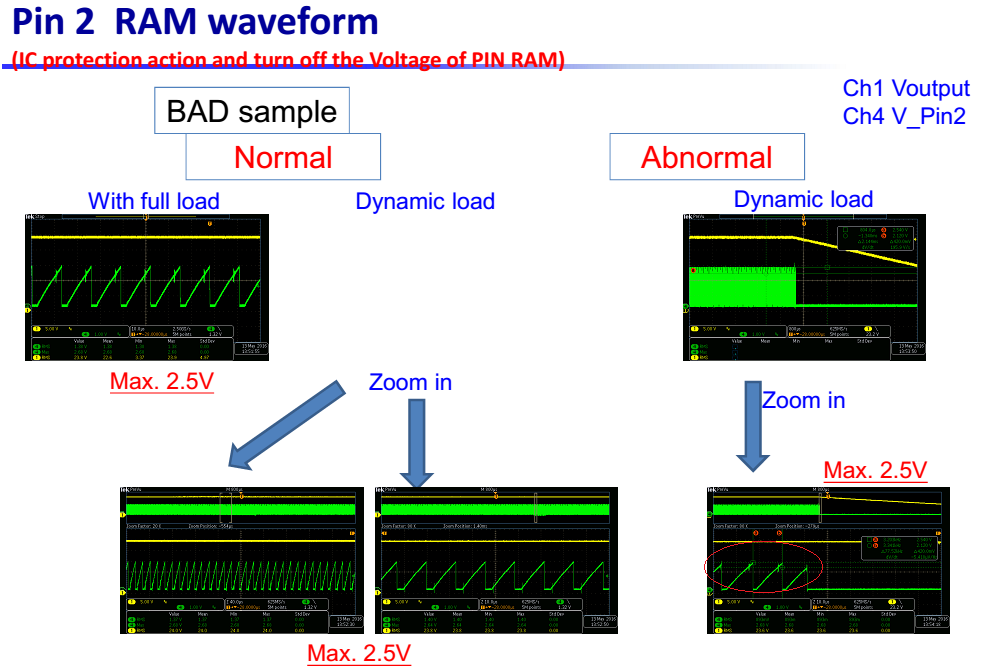

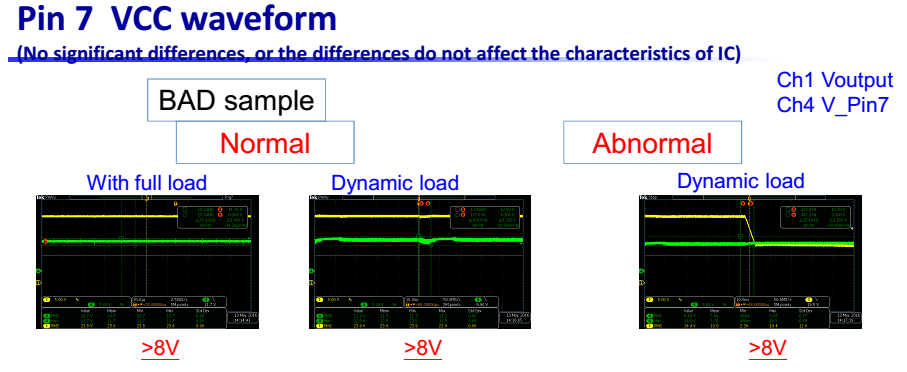

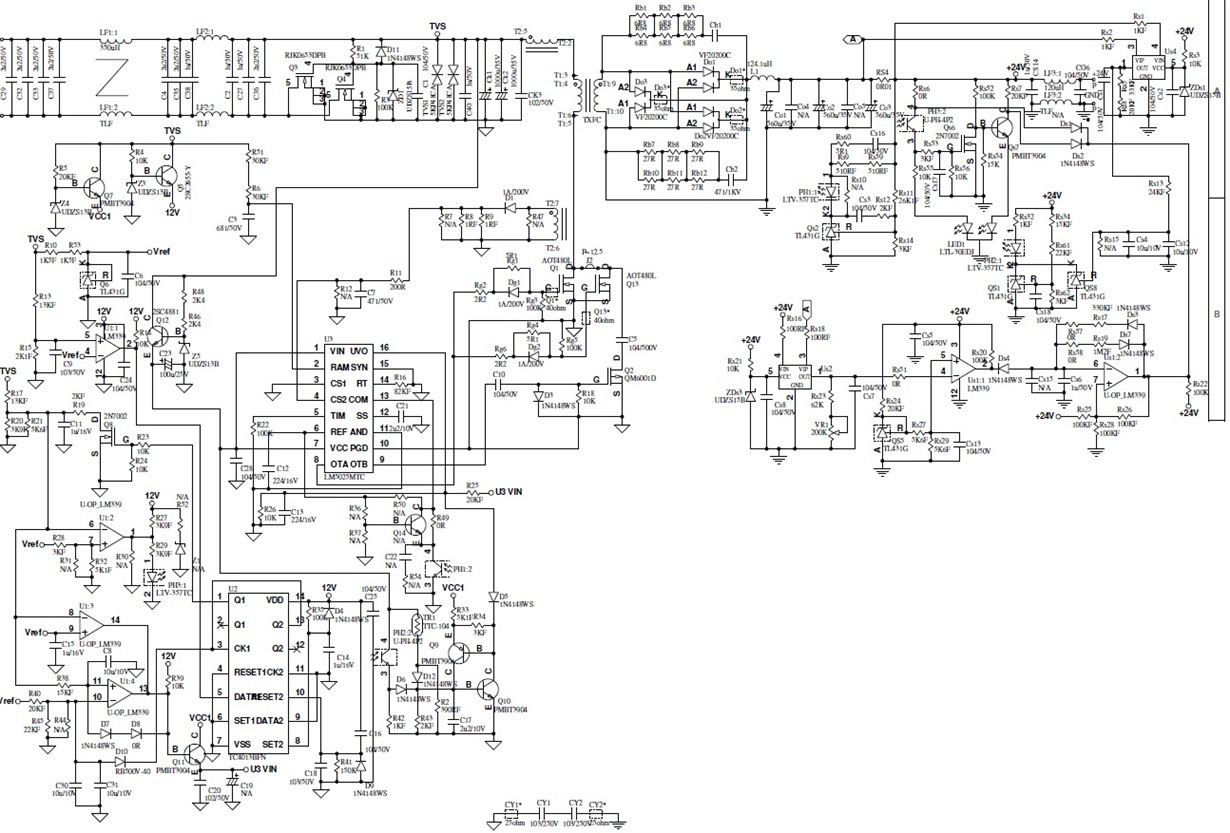

My customer currently use LM5025, test dynamic transient load, but have some issue.

Input range 10V~14V, Dynamic transient load(0~4.5A; 50mS ON/ OFF),

occur fail abnormal (@ input 10V), IC occur latch up and no output.

If ok, please let me know which part can effect RAMP pin occur fail abnormal, thanks.

Currently decreas dead time, can reduce RAMP fail, why?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.