Hi Team,

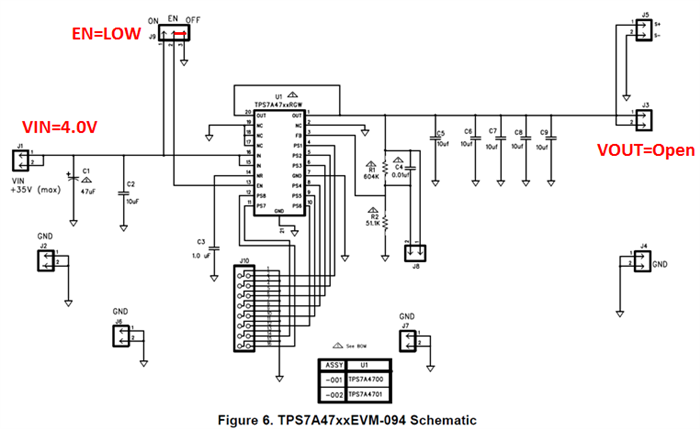

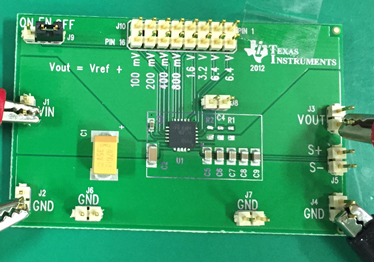

We are evaluating TPS7A4700EVM.

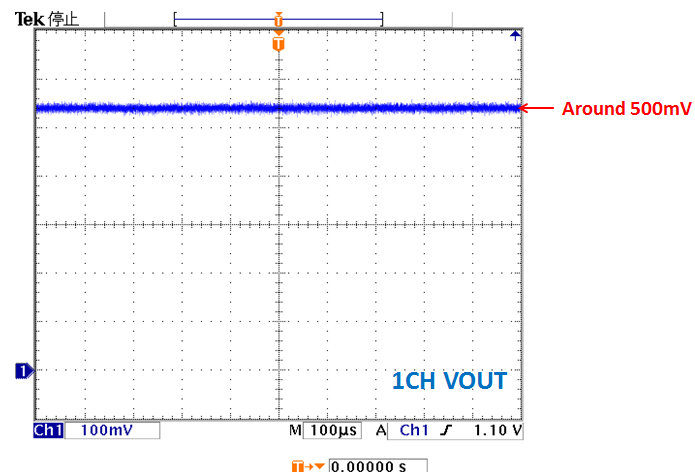

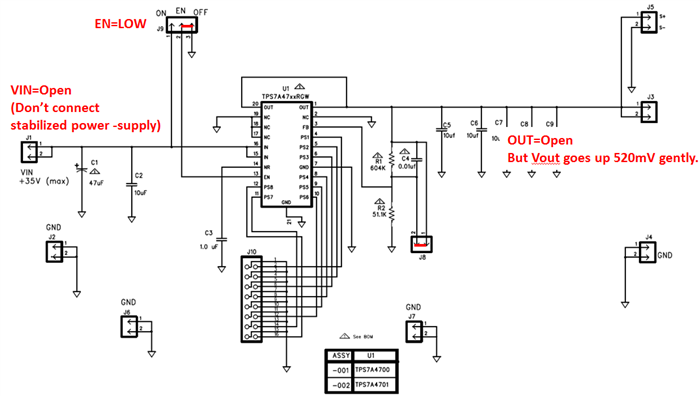

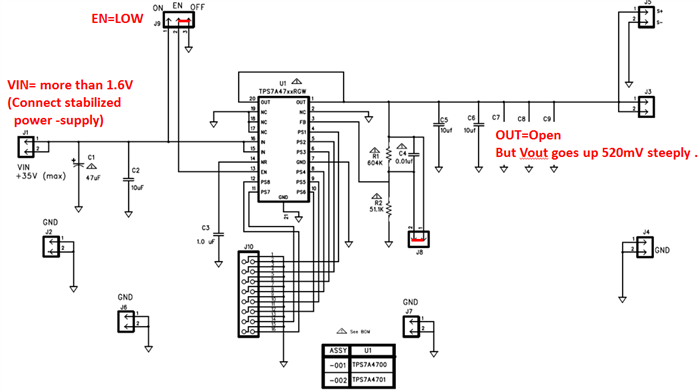

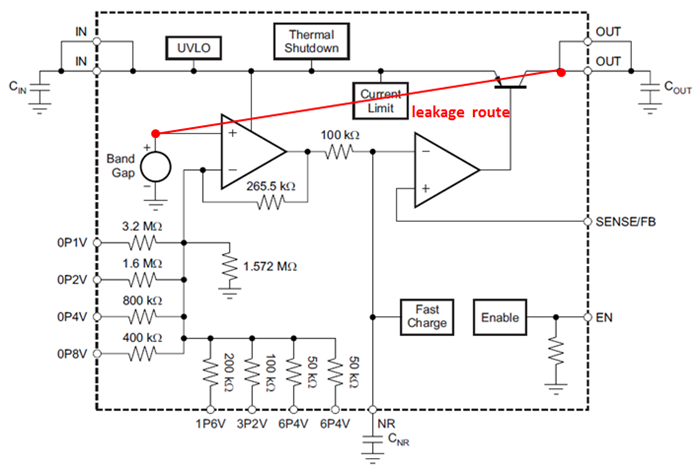

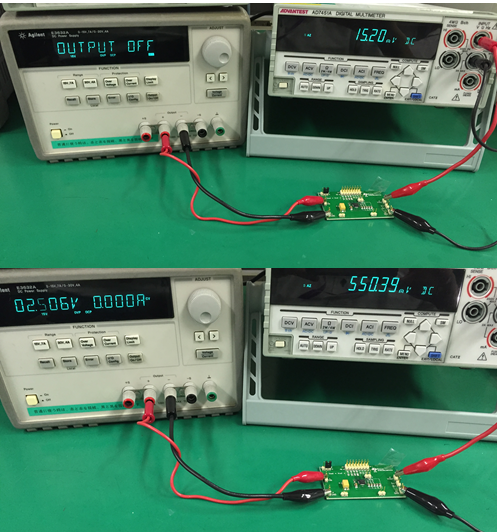

Then, output voltage is around 500mV at the shutdown (EN=Low).

(Please refer to the following waveform.)

Is this behavior right?

If yes, could you please let us know this cause and if you have any workaround?

Regards,

Kanemaru